LC5768MC-75F256C CPLD: Mga tampok, specs, pakinabang at aplikasyon

Ipinapaliwanag ng gabay na ito ang LC5768MC-75F256C, isang maliit ngunit malakas na chip na ginawa ng semiconductor ng lattice.Ipinapakita nito kung ano ang ginagawa ng chip, kung paano ito gumagana, kung paano ito i -program, at kung saan maaari itong magamit.Kung naghahanap ka ng isang chip na humahawak ng mga gawain sa lohika, gumagamit ng mababang lakas, at gumagana sa maraming mga aparato, ang gabay na ito ay makakatulong sa iyo na maunawaan kung bakit ang LC5768MC-75F256C ay isang mahusay na pagpipilian.Catalog

Ano ang LC5768MC-75F256C?

Ang LC5768MC-75F256C ay isang mataas na pagganap na kumplikadong programmable logic device (CPLD), bahagi ng ISPXPLD 5000MC pamilya.Ang aparatong ito ay dinisenyo sa paligid ng isang 1.8V core architecture at nagbibigay ng matatag na lohika density, pagsasama ng 768 macrocells.Bilang isang miyembro ng serye ng 5000MC, kumakatawan ito sa mga advanced na solusyon sa CPLD ng Lattice na nag-aalok ng maaasahang kontrol sa tiyempo, mahusay na pagpapatupad ng lohika, at mababang operasyon ng kuryente, na na-optimize para sa naka-embed at high-speed digital system.Ang pamilya ng ISPXPLD 5000MC ay nagpapabuti sa mga kakayahan ng tradisyonal na mga CPLD sa pamamagitan ng pagpapakilala ng mga bloke ng multi-function (MFB) at nababaluktot na suporta sa I/O, na ginagawa ang LC5768MC-75F256C isang solidong pagpipilian para sa nasusukat na pagsasama ng logic.Sa napatunayan na pagiging maaasahan at arkitektura na pinasadya para sa deterministikong pagganap, ang aparatong ito ay nagsisilbing isang maaasahang bloke ng gusali sa digital na disenyo.

Naghahanap ng LC5768MC-75F256C?Makipag -ugnay sa amin upang suriin ang kasalukuyang stock, oras ng tingga, at pagpepresyo.

LC5768MC-75F256C Mga Tampok

At 768 Macrocells (arkitektura na nakabase sa MFB)

Isinasama ng aparato ang 768 macrocells na naayos sa advanced na mga bloke ng multi-function (MFB), na sumusuporta sa lohika ng high-density na may naka-embed na aritmetika at mga kakayahan sa memorya.Pinapayagan ng mga MFB na ito ang nababaluktot na pagsasaayos para sa lohika, dual-port SRAM, FIFO, at CAM function.

At 1.8V Core boltahe (variant ng MC)

Ang variant ng MC-Series na ito ay nagpapatakbo ng isang 1.8V core, na nag-aalok ng mas mababang pagkonsumo ng kuryente para sa mga portable at mataas na kahusayan na disenyo.Sa kabila ng mababang boltahe, pinapanatili nito ang matatag na pagganap at density ng lohika.

At 7.5 pagkaantala sa pagpapalaganap (bilis ng grade -75)

Nakakamit nito ang isang maximum na pag-antala ng pagpapalaganap ng pin-to-pin na 7.5 nanosecond, na ginagawang angkop para sa katamtaman- hanggang sa high-speed digital application.Ang -75 bilis ng grade ay nagbabalanse ng kapangyarihan at bilis sa mga naka -embed na system.

At 193 Programmable I/O pin

Nag -aalok ang chip ng 193 I/O pin na sumusuporta sa maraming mga pamantayan at protocol ng boltahe.Ang mga pin na ito ay ganap na ma -program at pinapayagan ang nababaluktot na pakikipag -ugnay sa iba pang mga lohika o analog na aparato.

At Superwide Logic Support (Hanggang sa 136 Input bawat Block)

Sinusuportahan ng bawat MFB ang napakalawak na pag -andar ng lohika na may hanggang sa 136 na mga signal ng pag -input, na nagpapagana ng kumplikadong lohika ng kumbinasyon sa mas kaunting mga antas ng lohika.Binabawasan nito ang pagkaantala ng pagpapalaganap at pinapasimple ang synthesis ng lohika.

At Naka-embed na dual-port SRAM, FIFO, at suporta sa ternary cam

Ang mga MFB ay mai -configure upang kumilos bilang SRAM (solong/dual port), FIFO, o memorya ng memorya ng ternary na memorya.Ang kakayahang umangkop na ito ay nagbibigay-daan sa disenyo ng lohika na mayaman sa memorya sa isang compact na CPLD.

At On-chip pll (sysclock ™)

Sinusuportahan ng built-in na PLL ang pagdami ng orasan/dibisyon mula sa 1 × hanggang 32 ×, paglilipat ng phase, at panlabas na puna.Tumutulong ito sa pamamahala ng tiyempo at skew sa buong high-speed na magkakasabay na mga sistema.

At Wide I/O Standard Support (SYSIO ™)

Sinusuportahan ng mga bloke ng I/O ang isang malawak na hanay ng mga pamantayan sa pag -sign kasama ang LVCMOS, LVTTL, SSTL, HSTL, GTL+, LVDS, at LVPECL.Pinapayagan nito ang halo-halong boltahe at pagkakaiba-iba ng senyas sa isang solong aparato.

At In-System Programmability (ISPXP ™)

Sinusuportahan ng aparato ang programming ng in-system sa pamamagitan ng IEEE 1532 o interface ng sysconfig.Maaari itong i -reprogrammed sa board nang hindi tinanggal ito, pagpapagana ng mga pag -update ng disenyo at muling pagsasaayos ng patlang.

At Pagsubok sa Boundary Scan (IEEE 1149.1 Sumunod)

Pinapayagan ng buong suporta sa pag-scan ng Boundary ng JTAG ang matatag na pagsubok sa antas ng board at pag-debug.Tinitiyak nito ang pagsunod sa mga modernong kinakailangan sa pagsubok at pinapasimple ang pagpapatunay sa paggawa.

At 5v Tolerant I/o

Sa kabila ng isang 1.8V core, ang mga bangko ng I/O ay mapagparaya ng 5V signal, na sumusuporta sa mga interface ng boltahe ng legacy.Nagpapabuti ito ng pagiging tugma sa mga mas matatandang sistema at mga halo-halong boltahe na kapaligiran.

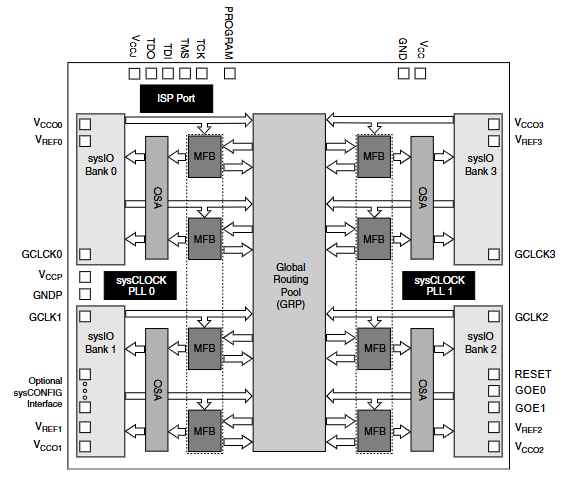

ISPXPLD 5000MX/5000MC block diagram

Ang block diagram ng LC5768MC-75F256C sa ISPXPLD 5000MX/5000MC pamilya ay nagha-highlight kung paano nakabalangkas ang chip upang mahawakan ang mga naka-program na gawain ng lohika.Sa gitna ay ang pandaigdigang ruta ng pool (GRP), na kumikilos bilang pangunahing hub ng koneksyon, na nag -uugnay sa iba't ibang mga lohika at functional blocks upang ang mga signal ay maaaring lumipat nang mahusay sa buong aparato.Sa magkabilang panig ng GRP ay dalawang phase-lock loops (PLL0 at PLL1), bahagi ng SysClock system.Ang mga ito ay bumubuo ng tumpak at adjustable na mga signal ng orasan na makakatulong na mapanatili ang katumpakan ng tiyempo para sa mga operasyon na may mataas na bilis sa buong chip.

Sa paligid ng GRP at PLLS ay apat na mga bangko ng Sysio.Ang bawat bangko ay naglalaman ng mga naka-configure na mga arrays ng system (CSA) at mga bloke ng multi-function (MFB).Ang CSAS ay humahawak ng pangunahing pagproseso ng lohika, habang sinusuportahan ng MFBS ang mas advanced na mga tampok tulad ng mga operasyon sa matematika at mga pag -andar ng memorya.Ang pag -aayos na ito ay nagbibigay sa aparato ng malakas na kakayahang umangkop sa I/O at ginagawang mas madali ang sukat para sa iba't ibang mga aplikasyon.Ang mga koneksyon sa kapangyarihan at orasan ay malinaw na ipinapakita sa diagram.Maramihang mga VCC, VREF, at GND pin ay ipinamamahagi upang mapanatili ang matatag na kapangyarihan sa buong chip.Ang mga pandaigdigang pag -input ng orasan (GCLK0 hanggang GCLK3) ay nagbibigay -daan sa mga panlabas na orasan na pakainin ang system at magtrabaho kasama ang GRP at PLLS.

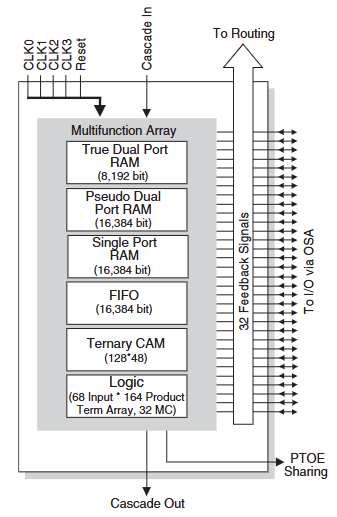

Multi-function block (MFB) diagram

Ang multi-function block (MFB) sa LC5768MC-75F256C ISPXPLD 5000MX/5000MC ay pinagsasama ang parehong mga pag-andar ng memorya at lohika upang suportahan ang nababaluktot na mga pangangailangan sa disenyo.Sinusuportahan nito ang ilang mga uri ng memorya, kabilang ang True Dual Port Ram (8,192 bits), Pseudo Dual Port Ram, FIFO, at Single Port Ram (bawat isa hanggang sa 16,384 bits), kasama ang Ternary Cam (128 × 48).Ang mga pagpipilian sa memorya ay ginagawang kapaki -pakinabang ang MFB para sa data buffering, pansamantalang imbakan, at mabilis na lookup ng data.

Ang MFB ay mayroon ding malakas na kakayahan sa lohika.Kasama dito ang isang 68-input sa pamamagitan ng 164-product term array at 32 macrocells, na pinapayagan itong magsagawa ng mga kumplikadong operasyon ng lohika.Gumagamit ito ng maraming mga input ng orasan (CLK0 hanggang CLK3) at isang signal ng pag -reset upang makontrol ang tiyempo at operasyon.Upang mapalawak ang pag -andar, pinapayagan ng mga cascade in/out port ang mga MFB na magkakonekta nang magkasama sa mga bloke.Ang interface ng QSA (Quad System Array) ay nag -uugnay sa MFB sa mga bangko ng I/O para sa mabilis na komunikasyon sa mga panlabas na sistema.Sa madaling sabi, ang MFB ay isang malakas, nababaluktot na yunit na humahawak sa parehong mga gawain ng memorya at lohika, na tumutulong sa aparato na mahusay na gumanap sa mga naka-embed at high-speed na aplikasyon.

LC5768MC-75F256C Mga pagtutukoy

|

I -type |

Parameter |

|

Tagagawa |

Lattice Semiconductor Corporation |

|

Serye |

ISPXPLD® 5000 |

|

Packaging |

Bulkan |

|

Bahagi ng Bahagi |

Aktibo |

|

Uri ng Programmable |

Sa system programmable |

|

Pagkaantala ng oras tpd (1) max |

7.5 ns |

|

Supply ng Boltahe - Panloob |

1.65V ~ 1.95V |

|

Bilang ng mga elemento/bloke ng lohika |

24 |

|

Bilang ng mga macrocells |

768 |

|

Bilang ng I/O. |

193 |

|

Temperatura ng pagpapatakbo |

0 ° C ~ 90 ° C (TJ) |

|

Uri ng pag -mount |

Surface Mount |

|

Package / Kaso |

256-BGA |

|

Package ng aparato ng supplier |

256-FPBGA (17x17) |

LC5768MC-75F256C Application

1. telecommunication at networking

Ang LC5768MC-75F256C ay mainam para magamit sa mga istasyon ng base, mga switch ng telecom, at mga yunit ng optical network, kung saan kinakailangan ang high-speed at deterministic na lohika.Ang naka-embed na memorya at suporta ng multi-boltahe I/O ay nagbibigay-daan sa pagproseso ng protocol, pag-frame ng data, at mga gawain ng kontrol ng mababang-latency.

2. Komunikasyon ng data at imbakan

Ang CPLD na ito ay angkop para sa mga router, RAID Controller, at mga disk-array system na nangangailangan ng mahusay na paghawak ng data at pagproseso ng mabilis na signal.Ang dual-port na SRAM at suporta ng FIFO ay nagbibigay ng buffering at flow control na kinakailangan sa mga high-throughput na kapaligiran.

3. Protocol processors at mga interface ng bus

Sa mahuhulaan na tiyempo at mga mapagkukunan ng lohika na may mataas na density, ang LC5768MC ay higit sa pagpapatupad ng mga tulay ng bus, mga interface ng backplane, at mga decoder ng protocol.Pinapayagan nito ang mabilis na mga tugon ng lohika at sumusuporta sa walang tahi na pagsasama sa maraming mga pamantayan sa pag -sign.

4. Mga Sistema ng Kontrol ng Pang -industriya at IoT

Sa pang -industriya na automation, ang aparato ay ginagamit para sa pagsubaybay, kontrol ng makina, at pagkakasunud -sunod ng lohika.Ang kakayahang instant-on nito, mababang draw draw, at matatag na mga tampok ng I/O ay angkop para sa mga IoT node at naka-embed na mga magsusupil.

5. Consumer at Medical Electronics

Ang mga compact na bakas ng paa at mayaman na lohika-mixed-memory na kakayahan ay ginagawang mahalaga ang CPLD sa mga portable na medikal na instrumento at elektronikong consumer.Pinangangasiwaan nito ang control ng system, pamamahala ng interface, at pagkakasunud-sunod ng kuryente sa mga disenyo na may sukat at sensitibo sa enerhiya.

LC5768MC-75F256C Mga katulad na bahagi

|

Tampok |

LC5768MC-75F256C |

LC5768MV-75F484C |

LC5768MV-75FN256C |

LC5768MV-5F484C |

|

Pamilya |

ISPXPLD 5000MC |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

|

Pangunahing boltahe |

1.8v |

3.3v |

3.3v |

3.3v |

|

Macrocells |

768 |

768 |

768 |

768 |

|

Max Frequency |

~ 150MHz |

~ 150MHz |

~ 150MHz |

~ 200–250MHz |

|

Pag -antala ng pagpapalaganap (TPD) |

7.5ns |

7.5ns |

7.5ns |

5ns |

|

Uri ng Package |

256-bola BGA |

484-ball BGA |

256-bola BGA |

484-ball BGA |

|

Package Code |

F256C |

F484C |

Fn256c |

F484C |

|

Bilangin ko |

193 |

317 |

193 |

317 |

|

In-system na Programmable |

Oo |

Oo |

Oo |

Oo |

|

Naka -embed na suporta sa memorya |

Oo (sram/fifo/cam) |

Oo |

Oo |

Oo |

|

Jtag (IEEE 1149.1) |

Suportado |

Suportado |

Suportado |

Suportado |

|

Instant-on |

Oo |

Oo |

Oo |

Oo |

|

Application |

Mababang lakas, siksik na lohika |

Mataas na I/O, Pangkalahatang Cpld |

Compact 3.3V Logic |

Mataas na bilis ng 3.3V na lohika |

LC5768MC-75F256C Mga Hakbang sa Programming

1. Ihanda ang iyong board at mga tool

Ikonekta ang LC5768MC-75F256C sa iyong PC gamit ang isang katugmang programming cable tulad ng lattice HW-USBN-2B.Siguraduhin na ang mga linya ng JTAG ay maayos na na -ruta at ang mga resistors ng pagtatapos (hal., 4.7kΩ sa TCK) ay nasa lugar upang matiyak ang matatag na komunikasyon.

2. Bumuo ng programming file

Gumamit ng lattice diamante o ISPVM software upang makatipon ang iyong disenyo at i -export ang isang Jedec (.jed) programming file.Ang file na ito ay naglalaman ng kumpletong bitstream na isusulat sa memorya ng pagsasaayos ng CPLD.

3. Ilunsad ang programming software

Buksan ang tool ng Diamond Programmer o ISPVM System sa iyong PC at i -verify na ang iyong programmer ay maayos na napansin.Piliin ang aparato ng LC5768MC-75F256C mula sa listahan upang simulan ang pag-setup.

4. Magsagawa ng In-System Programming (ISP)

Gamitin ang interface ng JTAG (IEEE 1532) upang mai -load ang JEDEC file nang direkta sa aparato habang nananatiling naka -mount sa board.Ang bitstream ay naka-imbak sa panloob na memorya ng hindi pabagu-bago, na nagpapagana ng instant-on na pagsasaayos sa pagsisimula.

5. Patunayan at secure ang pagsasaayos

Matapos ang pag-programming, magsagawa ng isang operasyon sa pagbabasa upang kumpirmahin ang pagsasaayos ay matagumpay.Kung kinakailangan, buhayin ang security fuse upang i -lock ang aparato at maiwasan ang hindi awtorisadong reprogramming o reverse engineering.

6. I -configure at i -reset ang aparato

Kapag kumpleto ang programming, maaaring awtomatikong i -restart ang aparato, o maaari mong i -toggle ang programa o init pin upang pilitin ang isang pag -reload.Ang CPLD ay pagkatapos ay magpapatakbo batay sa bagong inilapat na pagsasaayos na may deterministic na oras ng pagsisimula.

7. Opsyonal: Reprogramming o pag -update ng patlang

Maaari mong i-reprogram ang LC5768MC-75F256C sa patlang gamit ang parehong interface ng JTAG para sa mga update o pagwawasto.Bilang karagdagan, ang interface ng SySconFig ™ ay nagbibigay -daan sa bahagyang muling pagsasaayos nang walang buong pagbibisikleta sa power sa mga advanced na aplikasyon.

LC5768MC-75F256C Mga kalamangan

At Mas mababang operasyon ng kuryente para sa portable at naka -embed na mga system

Kung ikukumpara sa maraming tradisyonal na CPLD na may mas mataas na mga voltages ng core, ang LC5768MC-75F256C's low-power 1.8V core ay nakakatulong na mabawasan ang pangkalahatang pagkonsumo ng kapangyarihan ng system.Ginagawa nitong kaakit-akit para sa mga application na pinatatakbo ng baterya o sensitibo sa init kung saan bagay ang thermal budget at enerhiya na kahusayan.

At Kakayahang instant-on

Hindi tulad ng maraming mga FPGA o mas malaking mga ma-program na aparato na nangangailangan ng panlabas na pagsasaayos sa bawat pagsisimula, ang CPLD na ito ay nag-aalok ng instant-on na pag-uugali, na nagpapahintulot upang maiwasan ang mga pagkaantala o ang pangangailangan para sa panlabas na memorya ng flash.Ito ay humahantong sa mas mabilis na oras-sa-operasyon at higit na pagiging maaasahan.

At Higit pang mahuhulaan na tiyempo kumpara sa FPGAs

Ang deterministikong pag-uugali ng tiyempo ng CPLD na ito, lalo na sa ilalim ng mabibigat na lohika o I/O na naglo-load, ay nagbibigay ng mas mahusay na kontrol kumpara sa madalas na variable na tiyempo ng mas malaking FPGA.Ginagawa nitong mas angkop para sa mga application na kritikal na oras tulad ng mga digital control loops, interface ng komunikasyon, at naka-synchronize na mga sistema ng lohika.

At Mahusay na curve ng pag -aaral at ecosystem ng disenyo ng disenyo

Para sa paglipat mula 22v10s, mas matandang pal/gals, o simpleng mga PLD, ang aparatong ito ay nag -aalok ng isang banayad na curve ng pag -aaral sa pamamagitan ng intuitive na mga tool ng disenyo ng lattice tulad ng Diamond at ISPVM.Maraming nakikinabang mula sa mas mabilis na prototyping at mas kaunting mga sakit sa ulo ng pagsasama.

LC5768MC-75F256C Mga Dimensyon ng Packaging

At Uri ng Package: Fine-pitch ball grid array

At Bilangin ng pin: 256 bola

At Laki ng pakete: 17mm × 17mm

At Taas ng pakete: Humigit -kumulang na 1.2mm

At Ball Pitch: Karaniwang fine-pitch karaniwang 0.8mm

LC5768MC-75F256C Tagagawa

Ang LC5768MC-75F256C ay ginawa ng Lattice Semiconductor Corporation, isang kumpanya na nakabase sa Estados Unidos na kinikilala para sa kadalubhasaan nito sa mababang lakas, maliit na footprint na mga aparato na lohika.Itinatag noong 1983 at headquartered sa Hillsboro, Oregon, ang sala -sala ay nakatuon sa paghahatid ng mga FPGA, CPLD, at mga kaugnay na tool sa pag -unlad na pinasadya para sa mga aplikasyon sa mga komunikasyon, computing, pang -industriya, automotiko, at merkado ng mga mamimili.Ang kumpanya ay kilala para sa mahabang lifecycles ng produkto, malawak na suporta sa tool ng disenyo, at maaasahang pag-programmability ng in-system sa mga pamilya ng aparato nito.Bilang orihinal na developer at tagapagtustos ng ISPXPLD® 5000MC pamilya, tinitiyak ng lattice ang matatag na dokumentasyon ng teknikal, suporta sa software, at pagkakaroon sa pamamagitan ng mga awtorisadong namamahagi at pangmatagalang mga kasosyo sa lifecycle.

Konklusyon

Ang LC5768MC-75F256C ay isang matalino at maaasahang CPLD na nag-aalok ng malakas na pag-andar ng lohika at memorya sa isang compact chip.Gumagamit ito ng kaunting lakas, nagsisimula agad, at gumagana sa maraming iba't ibang mga uri ng signal.Sa pamamagitan ng 768 macrocells, built-in na memorya, mabilis na orasan, at nababaluktot na mga pagpipilian sa pag-input/output, naaangkop ito sa mga produkto tulad ng mga aparato ng telecom, pang-industriya na makina, mga sistema ng imbakan, at mga elektronikong consumer.Ang madaling pag -programming, malakas na pagganap, at suporta para sa mga update ay ginagawang isang kapaki -pakinabang na solusyon para sa parehong mga bagong disenyo at pag -upgrade.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Maaari ko bang gamitin ang LC5768MC-75F256C sa mga aparato na pinapagana ng baterya o sensitibo sa enerhiya?

Oo, ang 1.8V core boltahe at mababang-lakas na disenyo ng LC5768MC-75F256C ay ginagawang angkop para sa portable, baterya na pinatatakbo, at thermally na napipilitan na mga kapaligiran, tulad ng mga IoT node o medikal na aparato.

2. Ang LC5768MC-75F256C ay katugma sa mga sistema ng Legacy 5V?

Oo.Kahit na sa mababang core boltahe nito, ang LC5768MC-75F256C ay nagtatampok ng 5V-tolerant I/O na mga bangko, tinitiyak ang pagiging tugma sa mga interface ng legacy at mga halo-halong sistema ng boltahe nang hindi nangangailangan ng karagdagang mga sangkap na nagbabago ng antas.

3. Anong uri ng mga tool sa pag-unlad ang suportado para sa programming ng LC5768MC-75F256C?

Ang LC5768MC-75F256C ay suportado ng lattice diamante, ISPVM system, at ang programmer ng brilyante.Ang mga tool na ito ay nagbibigay ng kumpletong suporta para sa disenyo, kunwa, programming, at pag-debug na angkop para sa parehong antas ng entry at advanced na mga gumagamit.

4. Ang LC5768MC-75F256C ay nangangailangan ng panlabas na memorya upang mapatakbo?

Walang panlabas na memorya ang kinakailangan para sa pagsasaayos.Ang LC5768MC-75F256C ay walang memorya ng memorya at sumusuporta sa kakayahan ng instant-on, na pinapayagan itong simulan ang operasyon kaagad pagkatapos ng power-up nang hindi nangangailangan ng panlabas na flash o EEPROM.

5. Ang LC5768MC-75F256C ay angkop para sa malupit na pang-industriya na kapaligiran?

Oo, na may matatag na pagganap ng lohika, malawak na pagpapaubaya ng boltahe, at maaasahang pag-uugali ng pagsisimula, ang LC5768MC-75F256C ay gumaganap nang maayos sa mga sistema ng kontrol sa industriya at pag-aautomat ng pabrika kung saan kinakailangan ang matatag na operasyon.

EPF8820ARC208-4 Gabay sa FPGA: Mga Tampok, Arkitektura, Aplikasyon, at Programming

sa 2025/07/11

EPF6016ATC144-2N FPGA: Mga Tampok, Programming, Aplikasyon, at Alternatibo

sa 2025/07/10

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147768

-

USB-C pinout at mga tampok

sa 2000/04/18 111996

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111351

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83758

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79555

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66955

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63098

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63029

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54095

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52176