EPF8820ARC208-4 Gabay sa FPGA: Mga Tampok, Arkitektura, Aplikasyon, at Programming

Ang artikulong ito ay tungkol sa EPF8820ARC208-4, isang espesyal na chip na ginamit sa electronics.Ipinapaliwanag nito kung ano ang ginagawa ng chip, kung paano ito gumagana, at kung saan maaari itong magamit.Malalaman mo ang tungkol sa mga bahagi nito, kung paano i -set up ito, at kung bakit ginagamit pa rin ito ngayon sa mga bagay tulad ng mga radio, machine, kotse, at marami pa.Ipinapakita rin nito kung paano ito inihahambing sa iba pang mga katulad na chips.Catalog

Ano ang EPF8820ARC208-4?

Ang EPF8820ARC208-4 ay isang legacy na aparato ng FPGA mula sa serye ng Flex 8000 na binuo ng Altera, na ngayon ay nasa ilalim ng Intel Programmable Solutions Group.Dinisenyo gamit ang isang arkitektura na nakabase sa CMOS SRAM, kabilang ito sa isang pamilya ng muling mai-configure na mga aparato ng lohika na minarkahan ng isang yugto sa pag-unlad na pag-unlad ng lohika.Ang serye ng Flex 8000 ay kinikilala para sa maraming nalalaman logic cell istraktura at scalable interconnect, na angkop para sa pangkalahatang-layunin na digital na pagsasama.Ang EPF8820ARC208-4 ay partikular na nahuhulog sa isang mid-speed grade variant sa loob ng seryeng ito, at mga kakayahan ng magkakaugnay.Ibinahagi nito ang arkitektura nito sa iba pang mga variant ng bilis ng bilis tulad ng ‑2, ‑3, at ‑5, na naiiba lalo na sa pagganap ng tiyempo.

Naghahanap para sa EPF8820ARC208-4?Makipag -ugnay sa amin upang suriin ang kasalukuyang stock, oras ng tingga, at pagpepresyo.

Mga tampok na EPF8820arc208-4

At Flex 8000 arkitektura

Ang EPF8820ARC208-4 ay itinayo sa arkitektura ng Flex 8000 ng Altera, na gumagamit ng pagsasaayos na batay sa SRAM para sa programmability na in-system.Nagbibigay ito ng isang epektibo at nababaluktot na solusyon para sa mga aplikasyon ng mid-range na logic density.

At Logic Density

Ang aparato na ito ay nagsasama ng 672 mga elemento ng lohika, na naghahatid ng humigit -kumulang na 8,000 magagamit na mga pintuan ng system.Nag -aalok ito ng isang angkop na balanse sa pagitan ng pagiging kumplikado at pagganap para sa naka -embed na kontrol, pandikit na lohika, at mga disenyo ng makina ng estado.

At 5V Core na may suporta sa Multivolt ™ I/O.

Ang pagpapatakbo sa isang 5V supply, sinusuportahan din ng aparato ang 3.3V at 5V I/O na pamantayan gamit ang teknolohiyang Multivolt ™ I/O.Ginagawa nitong madaling iakma para sa mga halo-halong sistema ng boltahe at interface ng legacy.

At In-circuit reprogrammable configuration

Ang EPF8820ARC208-4 ay batay sa SRAM at sumusuporta sa pagsasaayos ng in-circuit gamit ang panlabas na serial o kahanay na mga prom.Pinapayagan nito ang mabilis na pag -update ng disenyo at muling pagsasaayos nang hindi inaalis ang aparato mula sa circuit.

At Fasttrack Interconnect Ruta

Ang istraktura ng interconnect na fasttrack nito ay nagbibigay ng isang mahuhulaan, high-speed ruta na tela.Sinusuportahan ng arkitektura na ito ang mahusay na paglalagay ng lohika at kontrol sa tiyempo, na nagpapagana ng pagganap ng naka -streamline na disenyo.

At Magdala at cascade chain para sa aritmetika

Ang dedikadong dala at cascade chain ay nagpapaganda ng pagpapatupad ng mga function ng aritmetika tulad ng mga adders at counter.Ang mga tampok na ito ay nagbabawas ng pagkaantala ng lohika at gawing simple ang pagtatayo ng mga kumplikadong operasyon sa matematika.

At Pagsunod sa Bus ng PCI (Rev 2.2)

Ang aparatong ito ay sumusunod sa PCI Local Bus Specification Revision 2.2, na ginagawang angkop para magamit sa mga sistema na batay sa PCI.Sinusuportahan nito ang 5V-tolerant na mga kapaligiran sa pag-sign ng PCI.

At Suporta sa Boundary Scan ng JTAG

Ang EPF8820ARC208-4 ay may kasamang built-in na IEEE 1149.1 (JTAG) na mga kakayahan sa hangganan.Pinapadali nito ang pag-debug, pagsubok sa board, at pag-verify ng in-system nang hindi nangangailangan ng karagdagang circuitry.

At Programmable Sill Rate Control

Nagtatampok ang mga driver ng output nito na maaaring ma -program na kontrol ng rate ng pagpatay, na tumutulong upang mabawasan ang paglipat ng ingay.Ito ay kapaki-pakinabang sa mga disenyo ng high-speed para sa integridad ng signal.

At Mode na low-power standby

Dinisenyo para sa kahusayan ng kuryente, ang aparato ay kumonsumo ng mas mababa sa 0.5mA sa mode ng standby.Pinapayagan nito ang mga system na makatipid ng kapangyarihan sa panahon ng walang ginagawa o hindi aktibo na mga panahon.

At Temperatura ng pagpapatakbo: 0 ° C hanggang 70 ° C.

Ang sangkap ay nagpapatakbo ng maaasahan sa loob ng isang saklaw ng temperatura ng komersyal na 0 ° C hanggang 70 ° C.Ito ay mainam para sa paggamit ng pangkalahatang layunin sa mga kinokontrol na kapaligiran.

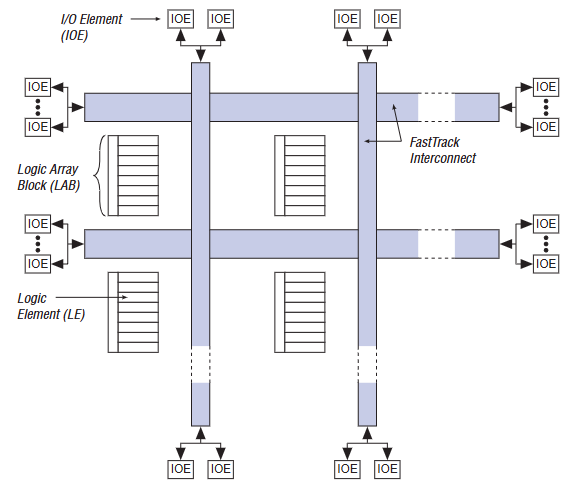

Flex 8000 block diagram

Inilalarawan ng diagram ang panloob na istraktura at kung paano pinoproseso ng FPGA ang lohika at koneksyon.Sa gitna ay ang mga lohika na mga bloke ng array (lab), na naglalaman ng maraming mga elemento ng lohika (LES).Ang mga LES na ito ay ma -program at maaaring mai -configure upang maisagawa ang isang malawak na hanay ng mga gawain ng lohika, na sumusuporta sa parehong kombinasyon at sunud -sunod na mga disenyo.Ang kakayahang umangkop na ito ay nagbibigay -daan para sa pasadyang pagpapatupad ng digital circuit.

Sa paligid ng mga lab ay ang mga elemento ng I/O (Ioes), na humahawak ng komunikasyon sa pagitan ng FPGA at mga panlabas na aparato.Sinusuportahan nila ang mga signal ng input, output, at bidirectional habang tinatanggap ang iba't ibang mga antas ng boltahe.Ang pagkonekta sa lahat ng mga bahagi ay ang FastTrack Interconnect, isang high-speed ruta system na nag-uugnay sa mga lab at Ioes nang mahusay.Tinitiyak ng setup na ito ang mabilis na paglipat ng data, makinis na pag -ruta ng signal, at maaasahang pagganap sa iba't ibang mga aplikasyon sa loob ng serye ng Flex 8000.

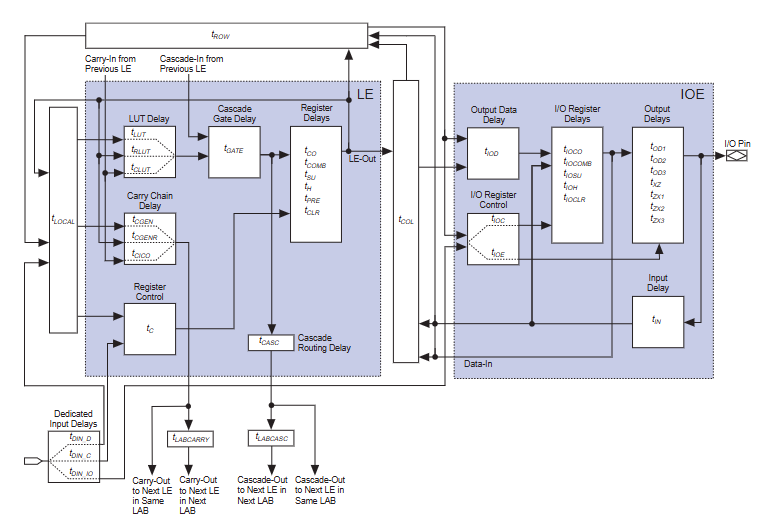

Flex 8000 mode ng tiyempo

Ang diagram ay nagtatampok kung paano nakakaapekto ang mga pagkaantala sa pagproseso ng lohika at daloy ng signal sa loob ng FPGA.Sa loob ng bawat elemento ng lohika (LE), ang mga kadahilanan ng tiyempo tulad ng Lookup Table (LUT) na pagkaantala, magdala ng pagkaantala ng chain, at magrehistro ng mga oras ng pag -setup/hold na matukoy kung gaano kabilis ang mga operasyon ng lohika na tumugon sa mga pagbabago sa pag -input.Ang mga panloob na pagkaantala ay mahalaga para sa pagpapanatili ng tumpak at matatag na operasyon, lalo na sa mga mabilis na paglilipat ng mga circuit.

Para sa mga operasyon ng I/O, ang mode ng tiyempo ay nagpapakita kung paano kumilos ang mga senyas habang pinapasok at lumabas ang FPGA.Kasama sa mga pangunahing punto ang pagkaantala ng output, pati na rin ang pag -setup ng input at mga oras ng paghawak, na tumutukoy kung gaano katagal ang mga panlabas na signal ay kailangang maging matatag para sa tamang pagkuha ng data.Inilarawan din ng diagram ang mga pagkaantala sa pagitan ng mga konektadong LES, kabilang ang mga dala at mga landas ng kaskad, na nakakaapekto sa daloy ng lohika sa buong aparato.Sama -sama, ang mga elemento ng tiyempo na ito ay nagsisiguro na naka -synchronize, maaasahan na pagganap sa buong arkitektura ng Flex 8000.

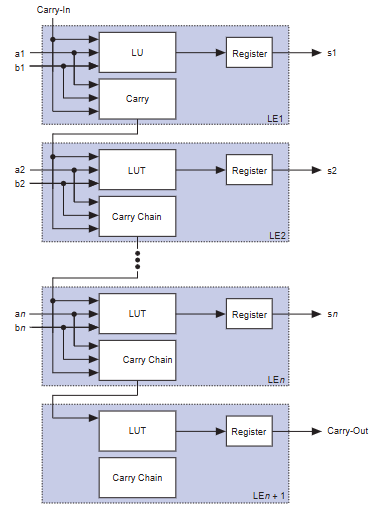

Flex 8000 Carry Chain Operation

Ang operasyon ng pagdala ng chain sa EPF8820arc208-4 Flex 8000 ay idinisenyo upang maisagawa ang mabilis na mga kalkulasyon ng aritmetika sa pamamagitan ng pag-uugnay ng maraming mga elemento ng lohika (LES) nang magkasama.Ang bawat LE ay naglalaman ng isang look-up table (LUT), isang dala ng logic circuit, at isang rehistro.Ang proseso ay nagsisimula sa isang signal ng dala-dala na pumapasok sa unang LE (LE1), na, kasama ang mga input A1 at B1, ay gumagawa ng isang kabuuan ng output (S1) at isang signal ng pagdala.

Ang signal na ito ay pagkatapos ay naipasa nang direkta sa susunod na LE sa chain (LE2, LE3, at iba pa), na pinapayagan ang bawat LE na makalkula ang sariling kabuuan ng output (S2 sa SN) gamit ang mga input nito at ang papasok na pagdala.Ang huling LE sa pagkakasunud-sunod ay bumubuo ng pangwakas na signal ng pagdala, na nakumpleto ang operasyon.Ang istraktura ng chain na ito ay nagbibigay-daan sa mabilis, mahusay na karagdagan, mainam para sa mga adders ng gusali, counter, at iba pang lohika na nakabatay sa aritmetika sa arkitektura ng Flex 8000.

EPF8820ARC208-4 Mga pagtutukoy

|

I -type |

Parameter |

|

Tagagawa |

Altera/Intel |

|

Serye |

Flex 8000 |

|

Packaging |

Tray |

|

Bahagi ng Bahagi |

Lipas na |

|

Bilang ng mga lab/clbs |

84 |

|

Bilang ng mga elemento/cell ng lohika |

672 |

|

Bilang ng I/O. |

152 |

|

Bilang ng mga pintuan |

8000 |

|

Boltahe - Supply |

4.75V ~ 5.25V |

|

Uri ng pag -mount |

Surface Mount |

|

Temperatura ng pagpapatakbo |

0 ° C ~ 70 ° C (TA) |

|

Package / Kaso |

208-BFQFP nakalantad na pad |

|

Package ng aparato ng supplier |

208-RQFP (28x28) |

EPF8820ARC208-4 Application

1. Digital Signal Processing (DSP) at Data-Path Control

Ang EPF8820ARC208-4 ay angkop para sa pagpapatupad ng mga pasadyang pag-andar ng DSP dahil sa katamtamang logic density at mahusay na arkitektura ng ruta.Maaari itong hawakan ang pagmamanipula ng data-path para sa mga operasyon tulad ng pag-filter, modulation, at pagbabagong-anyo ng mga high-speed digital signal.

2. Pasadyang interface ng bus at pag -off ng coprocessor

Sa pamamagitan ng malaking bilang ng mga I/O pin at suporta ng Multivolt ™, ang FPGA na ito ay madalas na ginagamit upang magdisenyo ng mga pasadyang mga interface ng peripheral o tulay na hindi magkatugma na mga antas ng lohika.Naghahain din ito bilang isang co-processor na nag-offload ng paulit-ulit na kontrol o mga gawain sa paghawak ng data mula sa pangunahing processor.

3. Pagproseso ng radyo na tinukoy ng software at komunikasyon

Ang kakayahang umangkop at kakayahang ma-reprograma ng aparato ay gawing mainam para sa mga application tulad ng software na tinukoy ng radyo (SDR), kung saan maaaring magbago ang mga scheme ng modulation o protocol.Maaari itong pabago -bago na hawakan ang pag -encode, pag -decode, at pamamahala ng signal sa mga layer ng komunikasyon.

4. ASIC prototyping at hardware emulation

Ang EPF8820ARC208-4 ay karaniwang ginagamit sa panahon ng prototyping phase ng pag-unlad ng ASIC.Ang reprogrammable arkitektura ay nagbibigay -daan sa mabilis na pagpapatunay, pagsubok, at simulation ng tiyempo ng mga kumplikadong digital na disenyo bago gumawa ng silikon.

5. Mga Pagkilala sa Voice at Encryption Engines

Ang FPGA na ito ay may kakayahang magpatupad ng medium-complexity logic tulad ng mga pipeline ng pagkilala sa boses at mga algorithm ng cryptographic.Ang pagkakaroon ng mga dala ng kadena at nakarehistro na I/OS ay nagsisiguro ng mabilis na pagkalkula at pagproseso ng signal ng mababang-latency na kinakailangan para sa mga naturang aplikasyon.

6. Mga Sistema ng Kontrol at Instrumentasyon ng Pang -industriya

Ang mahuhulaan na tiyempo, malaking mga kontrol ng magkasabay na mga kontrol, at nababaluktot na mga bloke ng lohika ay ginagawang angkop ang FPGA para sa mga sistemang pang -industriya.Madalas itong ginagamit sa ma-program na tiyempo, control ng estado-machine, at mga circuit ng conditioning ng signal.

7. Aerospace at Defense Embedded Systems

Ang aparatong ito ay ginagamit sa aerospace at defense electronics kung saan kinakailangan ang kakayahang umangkop sa pagsasaayos at maaasahang operasyon sa mga kinokontrol na kapaligiran.Sinusuportahan nito ang ligtas na pag-load ng firmware at nag-aalok ng mababang kapangyarihan ng standby, na nakikinabang sa mga aplikasyon ng kritikal na misyon.

8. Mga module ng Electronic Automotive

Sa automotive electronics, ang EPF8820ARC208-4 ay matatagpuan sa control modules paghawak ng lohika pagsasalin, diagnostics, o pagsasama ng data sa pagitan ng mga sensor at gitnang ECU.Ang muling mai -configure na kalikasan ay nagbibigay -daan sa mga pag -update at pagpapahusay kahit na pagkatapos ng pag -deploy.

9. Pagpapalit ng Telebisyon at Paghahawak ng Protocol

Sa mga sistema ng telecom, sinusuportahan ng FPGA na ito ang paglipat ng lohika, paghawak ng protocol, at pamamahala ng tiyempo.Maaari itong umangkop sa iba't ibang mga pamantayan sa pag -sign, tinitiyak ang pagiging tugma at pag -upgrade sa mga dynamic na network ng komunikasyon.

EPF8820ARC208-4 Katulad na mga bahagi

Narito ang isang talahanayan ng paghahambing ng EPF8820ARC208-4 at ang pinaka-kaugnay na mga katulad na bahagi mula sa parehong pamilya Flex8000:

|

Bahagi ng bahagi |

Bilis ng grado |

Uri ng Package |

I/o pin |

Mga elemento ng lohika |

Grado ng temperatura |

|

EPF8820ARC208-4 |

–4 (baseline) |

208-PIN QFP |

152 |

672 |

Komersyal |

|

EPF8820ARC208-2 |

–2 (mas mabagal) |

208-PIN QFP |

152 |

672 |

Komersyal (0-70 ° C) |

|

EPF8820ARC208-3 |

–3 (Katamtaman) |

208-PIN QFP |

152 |

672 |

Komersyal |

|

EPF8820ARC208-5 |

–5 (mas mabilis) |

208-PIN QFP |

152 |

672 |

Komersyal |

|

EPF8820AQC208-4 |

–4 |

208-PIN QFP (AQC) |

152 |

672 |

Komersyal |

|

EPF8820ARI208-4H |

–4 |

208-PIN QFP |

152 |

672 |

Pang -industriya (–40–85 ° C) |

EPF8820ARC208-4 Mga Hakbang sa Programming

1. Bumuo ng file ng pagsasaayos

Magsimula sa pamamagitan ng paglikha ng file ng pagsasaayos gamit ang software ng pag -unlad ng Altera tulad ng Max+Plus II o Quartus.Ang file na ito, karaniwang sa paligid ng 16KB ang laki, ay naglalaman ng kumpletong bitstream na kinakailangan upang tukuyin ang lohika at pagruruta ng EPF8820ARC208-4.

2. Piliin ang Scheme ng Pag -configure

Pumili ng isang naaangkop na pamamaraan ng pagsasaayos batay sa mga kinakailangan ng system: alinman sa aktibong serial/kahanay (kung saan kinokontrol ng FPGA ang paglo -load) o passive serial/kahanay (kung saan ang isang panlabas na magsusupil ay humahawak ng pagsasaayos).Ang mga pamamaraan ng passive ay mainam para sa mga system na nangangailangan ng pag-reprogramming o dynamic na pag-update.

3. Mag -set up ng mga koneksyon sa hardware

Ikonekta ang mga kinakailangang linya ng pagsasaayos tulad ng nconfig, conf_done, dclk, at data0 sa pagitan ng FPGA at ang iyong napiling aparato ng memorya ng pagsasaayos (hal., EPC1, EPC1213).Tiyakin na ang mga pull-up resistors at mga mapagkukunan ng orasan ay maayos na na-configure upang tumugma sa napiling mode ng pagsasaayos.

4. Power-on Initialization

Kapag ang system ay pinipilit o ang NConfig ay iginiit, ang FPGA ay pumapasok sa mode ng pagsasaayos at inilalagay ang lahat ng I/OS sa isang kondisyon ng tri-state.Handa na ang aparato na tanggapin ang data ng pagsasaayos batay sa scheme ng mga kable na ipinatupad mo.

5. Data ng Pag -configure ng Pag -load

Sa aktibong mode, ang FPGA ay kumukuha ng data nang direkta mula sa EPROM gamit ang panloob na oscillator.Sa passive mode, ang isang host processor o controller ng pagsasaayos ay nagbibigay ng data, at nakumpleto ang proseso kapag mataas ang signal ng conf_done.

6. Panloob na pagsisimula at paglipat sa mode ng gumagamit

Kapag ang bitstream ay ganap na na -load at ang conf_done ay iginiit, ang FPGA ay nagsasagawa ng panloob na pagsisimula, nagtatakda ng mga rehistro, at nagbibigay -daan sa User I/O.Ang aparato pagkatapos ay nagsisimula sa pagpapatupad ng disenyo ng lohika na na -program dito.

7. Opsyonal na muling pagsasaayos

Maaari kang mag-trigger ng isang cycle ng muling pagsasaayos sa pamamagitan ng paghila ng NConfig Low, na nag-reset ng aparato at muling pumasok sa mode ng pagsasaayos.Pinapayagan nito ang mabilis, in-system na pag-update o pagbawi ng lohika ng fallback, kasama ang buong proseso ng reprogramming na karaniwang nakumpleto sa ilalim ng 100 millisecond.

EPF8820ARC208-4 Bentahe

At Balanse na pagpipilian ng bilis ng bilis

Nag-aalok ang EPF8820ARC208-4 ng isang perpektong balanse sa pagitan ng pagganap at gastos, ginagawa itong mas mabilis kaysa sa mga mas mababang grade -2 o -3 na mga variant habang iniiwasan ang mas mataas na punto ng presyo ng –5 bilis ng grado.Pinapayagan nitong matugunan ang mga kinakailangan sa tiyempo nang walang labis na bayad para sa hindi nagamit na headroom.

At Mahuhulaan na mga pagkaantala sa pagruruta para sa control logic

Salamat sa pinong-grained na pahalang na pagruruta at pare-pareho ang mga landas sa pagkaantala, ang EPF8820ARC208-4 ay nagbibigay ng mahusay na mahuhulaan sa tiyempo.Ito ay kapaki-pakinabang sa mga disenyo na nakatuon sa control o mabibigat na estado

At Mabilis na pag-configure ng in-field

Ang istraktura na batay sa SRAM ay nagbibigay-daan sa muling pagsasaayos ng mas mababa sa 100 millisecond, pagpapagana ng mga update ng firmware at fallback logic sa mga live system.Mahalaga ito sa malayong o misyon-kritikal na mga aplikasyon kung saan dapat mabawasan ang downtime.

At Epektibo ang gastos

Para sa mga application na nangangailangan ng halos 8,000 mga pintuan ng system, ang EPF8820ARC208-4 ay nagbibigay ng tamang halaga ng lohika nang walang overhead ng mas malaking modernong FPGA.Pinapanatili nitong mababa ang gastos ng BOM habang natutugunan ang mga kinakailangan sa pag -andar.

At Pinasimple na pagsasama-sama ng boltahe

Sa pamamagitan ng katutubong suporta para sa parehong 3.3V at 5V I/O signaling, pinasimple ng aparato ang disenyo ng system kapag nakikipag-ugnay sa mga sangkap na TTL o halo-halong boltahe.Tinatanggal nito ang pangangailangan para sa mga karagdagang antas ng shifter, pag -save ng puwang ng board at gastos.

EPF8820ARC208-4 Mga Dimensyon ng Packaging

At Uri ng Package: 208-pin rqfp (hugis-parihaba na quad flat package)

At Laki ng katawan (D × E): 30.60 mm × 30.60 mm

At Package Outline (D1 × E1): Humigit -kumulang 28.00 mm × 28.00 mm

At Lead pitch (e): 0.50 mm

At Haba ng tingga (L): 0.60 mm tipikal (saklaw: 0.45 mm hanggang 0.75 mm)

At Lapad ng tingga (b): 0.17 mm tipikal (saklaw: 0.17 mm hanggang 0.27 mm)

At Ang anggulo ng tingga: 0 ° hanggang 8 °

At Uri ng pag -mount: Surface mount

EPF8820ARC208-4 Tagagawa

Ang EPF8820ARC208-4 ay ginawa ng Altera Corporation.Ang Altera ay orihinal na binuo ang Flex 8000 pamilya, kung saan kabilang ang aparatong ito, na nag-aalok ng isang muling mai-configure na arkitektura na pinasadya para sa mga aplikasyon ng mid-density na lohika.Noong 2015, si Altera ay nakuha ng Intel Corporation, at ang produkto ay patuloy na suportado sa ilalim ng Programmable Solutions Group ng Intel.Gayunpaman, noong 2024–2025, muling itinatag ng Intel ang Altera bilang isang standalone brand, na pinatunayan ang pokus nito sa pag-unlad ng FPGA at pangmatagalang suporta.Habang ang EPF8820ARC208-4 ay opisyal na inuri bilang hindi na ginagamit, ang pamana sa pagmamanupaktura nito ay nananatiling nakatali sa pamana ng pagbabago na maihatid ang maaasahang, nababaluktot, at malawak na pinagtibay na mga naka-program na solusyon sa lohika.

Konklusyon

Ang EPF8820ARC208-4 ay isang nababaluktot at maaasahang chip na nag-aalok ng isang mahusay na halo ng bilis, tampok, at gastos.Gumagana ito nang maayos sa maraming iba't ibang mga system dahil maaari itong ma -reprograma, sumusuporta sa iba't ibang mga boltahe, at mabilis na hawakan ang mga gawain sa matematika at kontrolin ang mga gawain.Ang disenyo nito ay tumutulong na siguraduhin na ang mga signal ay gumagalaw nang maayos at tumpak.Kahit na ito ay itinuturing na isang mas matanda o hindi naitigil na bahagi, kapaki -pakinabang pa rin ito sa mga system na nangangailangan ng matatag na pagganap at hindi madaling lumipat sa mga mas bagong chips.Ginagawa nitong isang matalinong pagpipilian para sa mga update, pag-aayos, o pangmatagalang suporta ng mas matandang elektronika.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Ang EPF8820arc208-4 ay nangangailangan ng panlabas na memorya ng pagsasaayos upang mag-boot up?

Oo, gumagamit ito ng panlabas na serial o kahanay na mga prom tulad ng EPC1 o EPC1213 upang mai -load ang data ng pagsasaayos sa panahon ng pagsisimula ng system o pag -reset.

2. Paano ko malalaman kung ang aking umiiral na disenyo ng board ay sumusuporta sa EPF8820ARC208-4 mode ng pagsasaayos?

Suriin ang iyong eskematiko para sa mga kinakailangang pin tulad ng nconfig, conf_done, dclk, at data0.Gayundin, tiyakin na ang iyong memorya ng pagsasaayos (tulad ng EPC1 o EPC1213) ay tumutugma sa napiling serial o kahanay na pamamaraan ng pagsasaayos.

3. Maaari ba akong magsagawa ng bahagyang muling pagsasaayos sa epf8820arc208-4?

Hindi, ang EPF8820ARC208-4 ay hindi sumusuporta sa bahagyang muling pagsasaayos.Ang anumang mga pag -update o pagbabago ng lohika ay nangangailangan ng isang buong pag -reload ng bits sa pamamagitan ng karaniwang pag -ikot ng pagsasaayos.

4. Mayroon bang panganib ng katiwalian ng bitstream sa panahon ng power-up?

Oo, kung ang tiyempo ng pagsasaayos o integridad ng signal ay hindi napapanatili nang maayos, maaaring mangyari ang katiwalian ng bitstream.Tiyakin ang malinis na pagkakasunud -sunod ng kuryente at wastong pagkabulok malapit sa mga linya ng FPGA at pagsasaayos.

5. Maaari ko bang gamitin ang EPF8820ARC208-4 para sa mga function ng cryptographic o secure na pagproseso?

Bagaman hindi pinapagod ng seguridad, ang aparato ay angkop para sa pagpapatupad ng pasadyang logic ng cryptographic tulad ng mga pangunahing engine ng pag-encrypt o pangunahing paghawak, ngunit kulang ito ng mga built-in na ligtas na tampok na matatagpuan sa mga modernong FPGA.

Paano maaaring gawing simple ng EPM7064AEFC100-10 ang iyong disenyo ng lohika

sa 2025/07/14

LC5768MC-75F256C CPLD: Mga tampok, specs, pakinabang at aplikasyon

sa 2025/07/10

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147780

-

USB-C pinout at mga tampok

sa 2000/04/18 112048

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111352

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83806

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79607

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66986

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63113

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63049

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54097

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52199