EPF6016ATC144-2N FPGA: Mga Tampok, Programming, Aplikasyon, at Alternatibo

Ang gabay na ito ay tungkol sa EPF6016ATC144-2N, isang uri ng chip na tinatawag na isang FPGA.Ginagamit ito sa mga digital system na kailangang maging kakayahang umangkop at madaling i -update.Ipinapaliwanag ng gabay kung ano ang ginagawa ng chip, kung paano ito gumagana, ang mga pangunahing bahagi at tampok nito, kung paano gamitin at i -program ito, kung saan magagamit ito, at kung bakit ito ay isang mahusay na pagpipilian ngayon.Catalog

Ano ang EPF6016ATC144-2N?

Ang EPF6016ATC144-2N ay isang miyembro ng pamilyang Flex 6000 FPGA na binuo ni Altera, na ngayon ay bahagi ng Intel.Itinayo sa SRAM-based na Reprogrammable Logic, ang aparatong ito ay inhinyero para sa kakayahang umangkop sa mga aplikasyon ng mid-density digital logic.Ginagamit nito ang arkitektura ng Optiflex, na pinagsasama ang mga bloke ng lohika ng mga lohika (LAB) at isang high-speed interconnect matrix upang maihatid ang mahusay na paggamit ng mapagkukunan at mabilis na pag-ruta ng signal.Sinusuportahan ng EPF6016ATC144-2N ang pag-configure ng in-system, na ginagawang perpekto para sa mga disenyo na nangangailangan ng mga pag-update o pagbabago sa post-deployment.Bilang bahagi ng serye ng Flex 6000, nag-aalok ito ng isang epektibong solusyon para sa pagpapalit ng tradisyonal na mga arrays ng gate habang pinapasimple ang siklo ng pag-unlad.

Naghahanap para sa EPF6016ATC144-2N?Makipag -ugnay sa amin upang suriin ang kasalukuyang stock, oras ng tingga, at pagpepresyo.

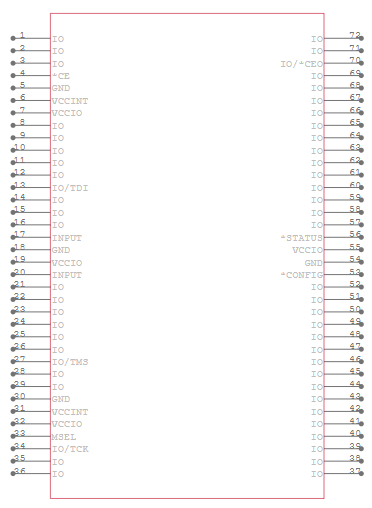

EPF6016ATC144-2N CAD MODELS

EPF6016ATC144-2N SYMBOL

EPF6016ATC144-2N Footprint

EPF6016ATC144-2N 3D Model

Mga tampok ng EPF6016ATC144-2N

At Kapasidad ng lohika

Nag-aalok ang EPF6016ATC144-2N sa paligid ng 16,000 mga pintuan ng system, na ipinatupad gamit ang 1,320 na mga elemento ng lohika (LES) sa buong 132 na mga bloke ng lohika (lab).Nagbibigay ito ng katamtamang pagiging kumplikado na angkop para sa mga mid-range na aplikasyon ng FPGA.

At I/o pin

Sinusuportahan nito ang hanggang sa 117 na hindi ma-configure na gumagamit ng I/O.Ang mga pin na ito ay nagbibigay -daan sa nababaluktot na koneksyon sa iba't ibang mga sangkap ng system at panlabas na aparato.

At Pangunahing boltahe

Ang core ay nagpapatakbo sa 3.3V na may isang saklaw na saklaw mula sa 3.0V hanggang 3.6V. Pinapayagan nito ang pagiging tugma na may karaniwang mga mababang sistema ng digital na boltahe.

At I/O boltahe

Ang tampok na multivolt I/O nito ay sumusuporta sa pakikipag -ugnay sa mga aparato gamit ang mga antas ng 3.3V o 2.5V.Pinapadali nito ang pagsasama sa mga halo-halong mga boltahe na kapaligiran.

At Temperatura ng pagpapatakbo

Ang karaniwang saklaw ng temperatura ng operating junction ay 0 ° C hanggang +85 ° C.Sinusuportahan nito ang mga karaniwang komersyal at pang -industriya na kapaligiran.

At Magtustos ng kasalukuyang

Gumuhit ito ng humigit -kumulang na 5mA sa panahon ng normal na operasyon at mas mababa sa 0.5mA sa mode ng standby.Makakatulong ito na mapangalagaan ang kapangyarihan sa mga disenyo na may kamalayan sa enerhiya.

At Bilis ng orasan (bilis ng grado –2n)

Sa pamamagitan ng isang -2 bilis ng grado, nakamit nito ang mga panloob na lohika frequency hanggang sa humigit -kumulang na 166MHz.Pinapayagan nito ang mabilis na pagkalkula sa pagproseso ng signal o control logic.

At Arkitektura

Batay sa arkitektura ng optiflex ng Altera, gumagamit ito ng lohika na batay sa LUT na may nakalaang mga mapagkukunan ng ruta.Nag -aalok ang arkitektura na ito ng mataas na lohika density at mahusay na pagganap.

At Interconnect ng Fasttrack

Ang Fasttrack ruta ng grid ay nagbibigay-daan sa mga landas ng signal ng mababang-latency at sumusuporta sa mga paglilipat ng data ng high-speed sa buong mga bloke ng lohika.Nag -aambag ito sa pare -pareho ang tiyempo at pagganap.

At In-circuit reconfiguration

Gumagamit ito ng pagsasaayos ng lohika na batay sa SRAM, na nagpapahintulot sa FPGA na ma-reprogrammed in-system.Sinusuportahan nito ang mga pag -update ng disenyo o dinamikong pagbagay sa hardware nang walang pag -alis.

At Jtag hangganan ng pag -scan

Kasama sa aparato ang IEEE 1149.1-sumusunod na JTAG border-scan logic.Pinapadali nito ang pag-debug at in-system testability ng mga board at interconnect.

At Suporta sa mainit na socketing

Maaari itong ligtas na maipasok o maalis habang pinapagana sa mga 3.3V system.Ang tampok na ito ay kapaki -pakinabang sa modular o serviceable na mga platform ng hardware.

At Pag -andar ng Pagsubok

Ang bawat yunit ay ganap na functionally nasubok bago ang kargamento.Tinitiyak nito ang kalidad at tinanggal ang pangangailangan para sa mga vectors na tinukoy ng gumagamit sa panahon ng pag-unlad.

At Pagiging tugma ng PCI

Ang aparato ay katugma sa PCI Local Bus Revision 2.2 para sa 5V na operasyon.Pinapayagan nito na magamit sa legacy na naka-embed na mga sistema ng PCI.

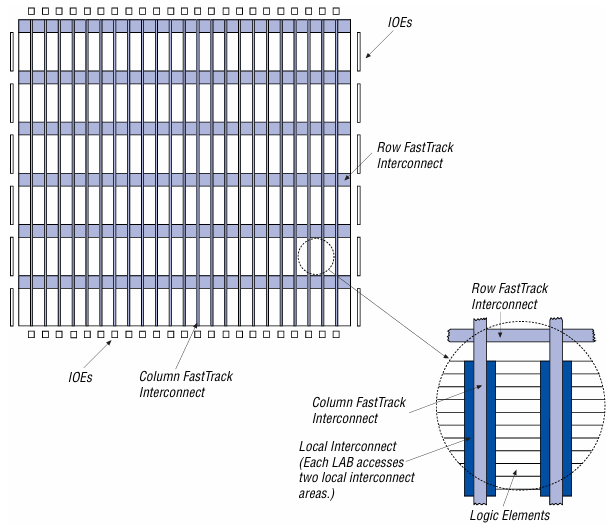

Optiflex Architecture Block Diagram

Ipinapakita ng diagram kung paano nakaayos at konektado ang mga panloob na bahagi ng FPGA.Sa gitna ay ang mga lohika na mga bloke ng array (lab), ito ang pangunahing mga yunit ng gusali ng chip.Ang bawat lab ay naglalaman ng maraming mga elemento ng lohika (LES) na nagsasagawa ng pangunahing mga digital na operasyon, tulad ng mga logic gate at flip-flops.Ang mga lab ay konektado sa pamamagitan ng isang lokal na magkakaugnay, na nagbibigay -daan sa lohika sa loob ng bawat bloke na magkasama nang maayos.Para sa mas malawak na komunikasyon sa buong chip, ang mga lab ay nag -uugnay sa hilera at haligi ng mga magkakaugnay na magkakaugnay, mabilis na mga landas ng signal na hayaan ang data na mabilis na lumipat mula sa isang bahagi ng chip patungo sa isa pa na may mababang pagkaantala.Sa paligid ng mga panlabas na gilid ng diagram ay ang mga elemento ng input/output (ioes).Kinokonekta nito ang panloob na lohika ng FPGA sa mga panlabas na aparato sa pamamagitan ng pag -convert sa pagitan ng mga antas ng lohika ng chip at ang mga antas ng boltahe na ginagamit ng iba pang hardware.Ang layout na ito, kasama ang mga modular na mga bloke at high-speed na mga landas sa pagruruta, ay sumasalamin sa kakayahang umangkop at pokus ng pagganap ng arkitektura ng optiflex.

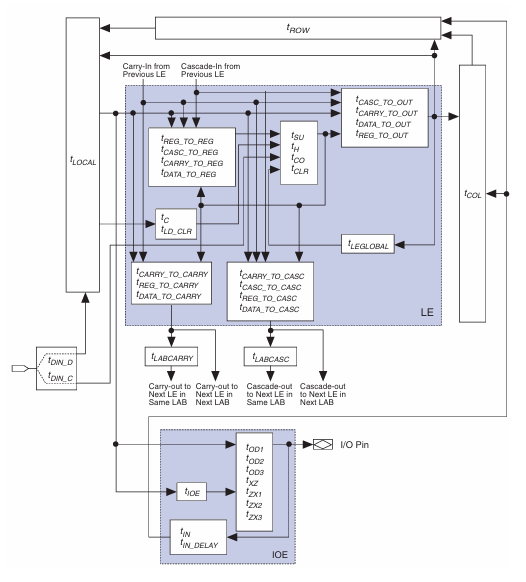

Flex 6000 modelo ng tiyempo

Ang modelo ng flex 6000 tiyempo ay nagpapakita kung paano lumipat ang mga signal at naantala habang naglalakbay sila sa FPGA.Sa gitna ng modelo ay mga elemento ng lohika (LES), na nagpoproseso ng mga data at mga signal ng kontrol na may tiyak na tiyempo.Ang bawat LE ay kumokonekta sa mga landas sa tiyempo tulad ng T_DATA_TO_REG at T_REG_TO_OUT, na tukuyin kung gaano katagal kinakailangan para sa mga signal na ipasok, maproseso, at lumabas sa lohika.

Sa tabi ng LES ay mga espesyal na landas na tinatawag na Lab Carry at Lab Cascade.Pinapayagan nito ang mga signal na ilipat nang pahalang sa pagitan ng mga elemento ng lohika sa parehong bloke, na sumusuporta sa mga mabilis na operasyon tulad ng mga karagdagan at paghahambing.Ang mga landas na ito ay mayroon ding sariling mga halaga ng tiyempo, tulad ng T_CARRY_TO_REG at T_CASC_TO_OUT, upang masukat ang mga pagkaantala sa mga operasyong ito.

Sa ilalim ng diagram, ang mga elemento ng input/output (IOEs) ay humahawak ng mga signal na papasok at labas ng chip.Kasama nila ang mga punto ng pagkaantala tulad ng T_IN_DELAY, na account para sa mga pagkakaiba -iba kapag tumatanggap ng data mula sa mga panlabas na aparato.

Kasama rin sa modelo ang mga landas sa pagruruta sa iba't ibang antas (t_local, t_row, t_col, at t_global) bawat isa ay kumakatawan kung gaano kalayo ang isang signal na naglalakbay at kung gaano karaming oras ang kinakailangan.Ang mga landas na ito ay tumutulong na maunawaan at pamahalaan ang mga pagkaantala sa iba't ibang bahagi ng chip, na ginagawang mas madali upang matugunan ang mga layunin sa pagganap at tiyempo.

EPF6016ATC144-2N Mga pagtutukoy

|

I -type |

Parameter |

|

Tagagawa |

Altera/Intel |

|

Serye |

Flex 6000 |

|

Packaging |

Tray |

|

Bahagi ng Bahagi |

Lipas na |

|

Bilang ng mga lab/clbs |

132 |

|

Bilang ng mga elemento/cell ng lohika |

1320 |

|

Bilang ng I/O. |

117 |

|

Bilang ng mga pintuan |

16000 |

|

Boltahe - Supply |

3V ~ 3.6V |

|

Uri ng pag -mount |

Surface Mount |

|

Temperatura ng pagpapatakbo |

0 ° C ~ 85 ° C (TJ) |

|

Package / Kaso |

144-LQFP |

|

Package ng aparato ng supplier |

144-TQFP (20x20) |

|

Base Number Product |

EPF6016 |

EPF6016ATC144-2N Application

1. Mga gawain sa Digital Signal Processing (DSP)

Sa pamamagitan ng 1,320 mga elemento ng lohika at mabilis na magkakaugnay, ang EPF6016ATC144-2N ay sumusuporta sa pagpapatupad ng maliit hanggang sa kalagitnaan ng saklaw na mga pag-andar sa pagproseso ng signal ng digital.Maaari itong magamit upang lumikha ng mga pasadyang fil filter, FFT cores, o kahanay na aritmetika na lohika para sa pagbabagong -anyo ng signal.Bagaman kulang ito ng dedikadong mga bloke ng DSP o naka-embed na mga multiplier, ang pangkalahatang layunin na lohika ay maaaring hawakan ang paulit-ulit na pagpaparami-naipon na mga operasyon na angkop para sa naka-embed na pagproseso ng audio, pag-filter ng data ng sensor, at paghuhubog ng alon sa mga sistema ng kontrol o komunikasyon.

2. naka -embed na kontrol at pang -industriya na automation

Ang aparato ay angkop para sa naka-embed na mga aplikasyon ng control sa mga pang-industriya na kapaligiran.Ang kakayahang makipag-ugnay sa halo-halong boltahe I/O (2.5 V at 3.3 V), ang matatag na operasyon nito sa ilalim ng karaniwang mga temperatura ng komersyal (0-85 ° C), at suporta para sa mainit na pag-iimpok ay ginagawang maaasahan para sa pagsasama sa mga programmable logic controller (PLC), mga yunit ng control ng motor, mga interface ng instrumento, at pangkalahatang kagamitan sa automation.Pinapayagan ng muling pagsasaayos para sa pangmatagalang kakayahang umangkop ng produkto, kung saan maaaring mai-update ang lohika nang hindi pinapalitan ang hardware.

3. Ang protocol protocol bridging at lohika ng interface

Salamat sa suporta ng multivolt I/O at mahusay na network ng pagruruta, ang EPF6016ATC144-2N ay maaaring magamit upang maipatupad ang mga pasadyang interface ng komunikasyon at mga convert ng protocol.Maaari itong bumuo ng mga uarts, SPI controller, o kahanay na mga tagasalin ng bus upang paganahin ang pakikipag -ugnayan sa pagitan ng mga mismatched digital system.Ang katamtamang bilang nito sa I/O (117 GPIO) at pamamahala ng panloob na orasan ay sumusuporta din sa pag-sign ng oras na sensitibo, na ginagawang angkop para sa mga kagamitan sa networking, pagtulad ng legacy bus, o bilang isang elemento ng logic na pandikit sa mas malaking mga sistema ng komunikasyon ng data.

4. Pagsubok sa antas ng board, pag-debug, at pagpapatunay

Sa pamamagitan ng built-in na JTAG hangganan-scan na kakayahan (IEEE 1149.1 na sumusunod), ang EPF6016ATC144-2N ay sumusuporta sa advanced na antas ng board-level nang hindi nangangailangan ng panlabas na lohika probes o nakakaabala na mga diagnostic.Maaari itong i-verify ang koneksyon sa I/O, makita ang bukas o maikling mga circuit, at magsagawa ng mga tseke ng in-system sa panahon ng paggawa o pagpapanatili ng larangan.Ang tampok na ito ay kapaki -pakinabang sa kumplikadong multilayer PCB o sa mga system kung saan ang tradisyonal na pag -access sa mga puntos ng pagsubok ay limitado o hindi praktikal.

EPF6016ATC144-2N Mga katulad na bahagi

|

Mga tampok |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

Tagagawa |

Altera |

Intel (Altera Legacy) |

Intel (Altera Legacy) |

|

Pamilya |

Flex 6000 |

Flex 6000 |

Flex 6000 |

|

Mga elemento ng lohika (LES) |

1,320 |

1,320 |

1,320 |

|

Bilang ng Gate (tinatayang.) |

16,000 |

16,000 |

16,000 |

|

Package |

100-pin TQFP |

100-pin TQFP |

144-PIN TQFP |

|

Gumagamit i/o pin |

81 |

81 |

117 |

|

Bilis ng grado |

-1 (pamantayan) |

-3n (mataas na bilis) |

-3n (mataas na bilis) |

|

Max clock frequency |

Mas mababa (karaniwang ~ 100 MHz) |

Mas mataas (hanggang sa ~ 166 MHz) |

Mas mataas (hanggang sa ~ 166 MHz) |

|

Uri ng Pag -configure |

Batay sa sram |

Batay sa sram |

Batay sa sram |

|

Boltahe ng supply ng kuryente |

3.3 v |

3.3 v |

3.3 v |

|

Mainit na socketing |

Oo |

Oo |

Oo |

|

Jtag/hangganan ng pag -scan |

Oo |

Oo |

Oo |

|

Mga Aplikasyon |

Pangunahing lohika, mga disenyo ng compact |

Mas mabilis na control logic, compact |

Mga sistema ng mataas na pagganap, mas maraming I/O. |

|

Pagkakaroon |

Lipas na |

Lipas na |

Lipas na |

EPF6016ATC144-2N Mga Hakbang sa Programming

1. Piliin ang mode ng pagsasaayos

Sinusuportahan ng EPF6016ATC144-2N ang pagsasaayos na batay sa SRAM, nangangahulugang nangangailangan ito ng pagprograma sa bawat power-up.Pinapayagan ng aparato para sa maraming mga scheme ng pagsasaayos, pinaka -karaniwang passive serial (PS) at passive kahanay na asynchronous (PPA).Ang mode ng pagsasaayos ay tinutukoy ng kung paano nakakonekta ang MSEL pin.Halimbawa, kapag ang MSEL ay nakatali nang mababa, inaasahan ng aparato ang data na maipadala sa pamamagitan ng panlabas na EEPROM (tulad ng EPC1) o isang pag -download ng cable.Ang pagpili ng tamang pamamaraan ng pagsasaayos ay nakasalalay sa disenyo ng system, batay sa EEPROM para sa awtomatikong boot-up, o batay sa cable para sa prototyping at pagsubok.

2. isama ang disenyo ng FPGA at makabuo ng isang file ng programming

Upang i -program ang FPGA, kailangan mo munang lumikha ng iyong disenyo ng hardware gamit ang Intel's Quartus o Legacy Max+Plus II na disenyo ng software.Pagkatapos ng compilation, ang tool ay bumubuo ng isang sof (SRAM object file) na kumakatawan sa naka -configure na lohika.Ang SOF na ito ay dapat na ma -convert sa isang format na katugma sa iyong napiling pamamaraan ng pagsasaayos:

• .RBF o .POF para sa mga aparato ng EEPROM (hal., EPC1).

• .ttf o .hex para sa microcontroller o kahanay na paglo -load.

Ang pag-convert ay ginagawa gamit ang built-in na file converter utility sa software ng disenyo.Tinitiyak ng hakbang na ito na ang bitstream ay na -format nang tama para sa FPGA upang bigyang -kahulugan.

3. I -program ang memorya ng pagsasaayos (kung gumagamit ng EEPROM)

Sa mga aplikasyon kung saan ginagamit ang isang serial na aparato ng pagsasaayos tulad ng isang EPC1, ang susunod na hakbang ay upang mai -load ang data ng pagsasaayos sa EEPROM.Ito ay karaniwang ginagawa gamit ang isang tool sa desktop programming (hal., Max+Plus II programmer o quartus programmer).Ang proseso ay nagsasangkot ng paglalagay ng EEPROM sa isang programming socket o pagkonekta nito sa circuit, pag-load ng naaangkop na file ng programming (karaniwang .POF o .RBF), at sinimulan ang siklo ng programa.Kapag na -program, ang EEPROM ay awtomatikong magbibigay ng data ng pagsasaayos sa FPGA sa tuwing pinapagana ng system, tinanggal ang pangangailangan para sa manu -manong reprogramming.

4. I -configure ang paggamit ng isang pag -download ng cable (passive serial)

Ang isang alternatibo sa eeprom-based boot-up ay gumagamit ng isang pag-download ng cable (tulad ng USB-Blaster o Byteeblaster) upang direktang i-configure ang FPGA.Sa pamamaraang ito, ikinonekta mo ang cable sa iyong PC at ang FPGA's NConfig, DCLK, data, at conf_done pin.Gamit ang quartus programmer, sinimulan mo ang proseso ng pagsasaayos, na kung saan ang mga pulses nconfig mababa upang magsimula.Ang tool pagkatapos ay nagpapadala ng data ng pagsasaayos ng serially sa pamamagitan ng linya ng data, na na -clocked ng DCLK.Kumpleto ang proseso kapag mataas ang conf_done, na nagpapahiwatig ng matagumpay na pagsasaayos at paglipat ng aparato sa mode ng gumagamit.

5. I -configure ang paggamit ng isang microcontroller (passive serial/kahanay)

Kung ang iyong system ay gumagamit ng isang naka -embed na microcontroller, maaari rin itong kumilos bilang master ng pagsasaayos ng FPGA.Sa pag -setup na ito, ang microcontroller ay iginiit ang NConfig na mababa upang i -reset ang FPGA, pagkatapos ay ilipat ang pagsasaayos ng bitstream sa pamamagitan ng data habang ang pag -toggling DCLK.Ang mga kinakailangan sa tiyempo ay dapat igalang, oras ng pag -setup ng data bago ang orasan at ang oras pagkatapos ay mabuti para sa matagumpay na pagsasaayos.Maaaring masubaybayan ng microcontroller ang NSTATUS at conf_done pin upang makita ang mga error sa pagsasaayos o kumpirmahin ang matagumpay na pagkumpleto.Ang pamamaraang ito ay nag -aalok ng buong kontrol sa proseso ng pagsasaayos at sumusuporta sa mga dynamic na pag -update sa larangan.

6. Subaybayan ang mga signal ng pagsasaayos

Sa panahon ng proseso ng pagsasaayos, ang FPGA ay nagbibigay ng puna sa pamamagitan ng mga status pin:

• Ang nStatus ay nagpapahiwatig ng pagtuklas ng error;Ito ay mababa kung ang isang kasalanan ay nangyayari (hal., CRC error o paglabag sa tiyempo).

• Ang conf_done ay mataas sa sandaling ang lahat ng mga bits ng pagsasaayos ay matagumpay na na -load at napatunayan.

Kung ang NSTATUS ay nananatiling mataas at conf_done na mga paglilipat nang mataas sa dulo ng pagkakasunud-sunod, awtomatikong pumapasok ang aparato sa mode ng gumagamit, kung saan nagiging aktibo ang tinukoy ng gumagamit.Mahalaga ang pagsubaybay sa signal na ito upang matiyak na matagumpay na nakumpleto ang proseso ng pagprograma.

7. Magsagawa ng muling pagsasaayos kung kinakailangan

Dahil ang EPF6016ATC144-2N ay nakabase sa SRAM, maaari itong mai-configure sa anumang oras sa pamamagitan ng pag-toggling ng NConfig pin mababa, na nag-reset ng aparato at i-restart ang pag-ikot ng pagsasaayos.Ang tampok na ito ay nagbibigay -daan para sa nababaluktot na pag -update ng system at mga pagbabago sa panahon ng operasyon nang walang pisikal na kapalit.Ang kakayahang muling mai-configure habang ang in-circuit ay sumusuporta din sa kalabisan, dynamic na pagpapalit ng pag-andar, o pagwawasto ng mga bug sa post-deployment.Ginagawa nitong lubos na angkop ang aparato para sa mga aplikasyon na nangangailangan ng kakayahang umangkop o kahabaan ng buhay.

8. Sundin ang mga kinakailangan sa tiyempo at elektrikal

Programming Ang EPF6016ATC1444-2N ay matagumpay na nangangailangan din ng pansin sa mga hadlang sa elektrikal at tiyempo.Ang pagsasaayos ng orasan (DCLK) ay dapat matugunan ang mga limitasyon ng dalas (hal., Karaniwan hanggang sa 10 MHz sa karaniwang mga mode ng serial).Ang aparato ay nangangailangan ng isang maikling pagkaantala (tungkol sa 200 ms) pagkatapos ng power-up para sa panloob na pag-reset ng power-on upang patatagin.Bilang karagdagan, ang lahat ng mga signal ng pagsasaayos ay dapat na malinis, walang ingay, at maayos na natapos.Kung gumagamit ng hot-socketing, dapat gawin ang pangangalaga upang matiyak ang integridad ng signal at wastong pagkakasunud-sunod ng kapangyarihan at I/O.

EPF6016ATC144-2N Bentahe

At Gastos-epektibo para sa mga disenyo ng mid-complexity

Ang EPF6016ATC144-2N ay tumatama sa isang balanse sa pagitan ng kakayahang magamit at pag-andar, na ginagawang perpekto para sa mga disenyo na nangangailangan ng higit na kakayahang umangkop kaysa sa naayos na lohika ngunit huwag bigyang-katwiran ang gastos o kapangyarihan sa itaas ng mga high-end na FPGA.

At Pinasimple na disenyo at pagsasama ng PCB

Kung ikukumpara sa mga mas mataas na density na FPGA na madalas na nangangailangan ng mga fine-pitch BGA packages, ang EPF6016ATC144-2N ay dumating sa isang karaniwang 144-pin TQFP package.Ang packaging na ito ay pinapasimple ang parehong disenyo at paggawa ng mga PCB dahil maiiwasan nito ang pangangailangan para sa mga advanced na tool ng layout, microvias, o magastos na mga board na may mataas na layer.Pinapabilis din nito ang paghuhugas ng kamay o pangunahing rework, na kapaki-pakinabang para sa mas maliit na mga koponan o lab na may limitadong mga kakayahan sa pagpupulong.

At Mababang peligro ng kabataan sa panahon ng paglawak

Dahil sa matagal na suporta nito sa mga aplikasyon ng pang-industriya ng Legacy, ang EPF6016ATC144-2N ay nananatiling magagamit sa maraming pangalawang merkado at malawak pa ring suportado sa disenyo ng software tulad ng Quartus II at Max+Plus II.Para sa mga kumpanya na nagpapanatili ng mga produktong pang-lifecycle tulad ng automation ng pabrika, mga sistema ng pagsukat, o mga module ng telecom, tinitiyak nito ang patuloy na pag-access sa kilalang-mahusay na silikon nang hindi na kailangang muling idisenyo ang hardware sa paligid ng mas bago, mas kumplikadong mga FPGA.

At Maaasahang pag -uugali

Hindi tulad ng ilang mga mas bagong mataas na pagganap na mga FPGA na nagpapatakbo sa masikip na mga margin at sensitibo sa pagbabago ng kapangyarihan at temperatura, ang EPF6016ATC144-2N ay matatag at mapagparaya sa mga karaniwang pagkakaiba-iba ng kapaligiran.Nagpapatakbo ito nang kumportable sa buong saklaw ng temperatura ng komersyal at sumusuporta sa hot-socketing, na ginagawang maaasahan sa mga modular o serviceable system.Ang pagiging maaasahan na ito ay ginagawang isang praktikal na pagpipilian para sa mga system na humihiling ng pare -pareho ang pagganap sa paglipas ng panahon at sa ilalim ng mga variable na kondisyon.

At Pangmatagalang katatagan ng disenyo

Sa mga senaryo kung saan ang pangmatagalang pagkakaroon at pag-freeze ng disenyo ay mas mahalaga kaysa sa pagganap ng paggupit, ang aparatong ito ay isang solidong kandidato.Kapag napatunayan ang lohika at naka -lock ang file ng pagsasaayos, ang buong sistema ay maaaring manatiling hindi nagbabago sa loob ng maraming taon, kahit na mga dekada.Ito ay isang pangunahing pakinabang sa aerospace, transportasyon, at mga aplikasyon ng militar kung saan ang pag -aaplay ng mga bagong bahagi ay mahal o hindi praktikal.

EPF6016ATC144-2N Mga Dimensyon ng Packaging

Uri ng Package: TQFP-144 (manipis na quad flat package)

Laki ng katawan: 20 mm × 20 mm

Pin pitch: 0.5 mm

Bilangin ng pin: 144 pin

Taas ng pakete: 1.0 mm

Uri ng lead frame: Ang Gull-Wing ay humahantong sa lahat ng apat na panig

Uri ng pag -mount: Surface-mount (SMT)

EPF6016ATC144-2N Tagagawa

Ang EPF6016ATC144-2N ay orihinal na ginawa ng Altera Corporation.Noong 2015, si Altera ay nakuha ng Intel Corporation, at ang aparato ay opisyal na nakalista sa ilalim ng Programmable Solutions Group ng Intel, na namamahala at sumusuporta sa mga linya ng produkto ng Legacy FPGA ng Altera.Bagaman ang EPF6016ATC144-2N ay bahagi ng isang ipinagpapatuloy na pamilya, ang Intel ay nananatiling pormal na tagagawa at tagapag-alaga ng aparatong ito, pinapanatili ang dokumentasyon, na-archive na suporta, at mga abiso sa lifecycle sa ilalim ng branding ng Intel.

Konklusyon

Ang EPF6016ATC144-2N ay isang nababaluktot at maaasahan na FPGA para sa maraming iba't ibang mga proyekto.Nag-aalok ito ng isang mahusay na halaga ng logic power, maraming mga input/output pin, at madaling pag-update ng in-system.Sinusuportahan ng disenyo nito ang mga halo-halong sistema ng boltahe, mabilis na paggalaw ng data, at reprogramming nang hindi tinanggal ito mula sa isang board.Madalas itong ginagamit sa mga bagay tulad ng mga control system, pagproseso ng signal, mga link sa komunikasyon, at kagamitan sa pagsubok.Sa pamamagitan ng malakas na suporta, mahabang pagkakaroon, at simpleng packaging, nananatili itong isang matalinong pagpipilian na nangangailangan ng isang epektibo at matatag na solusyon.

Datasheet PDF

EPF6016ATC144-2N Datasheets:

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Anong mga tool ang kailangan kong i-program ang EPF6016ATC144-2N ngayon?

Maaari mong gamitin ang Legacy Quartus II o Max+Plus II software para sa pag -unlad at pagsasama.Para sa programming, ang mga tool tulad ng USB-Blaster Cable at Quartus Programmer ay nananatiling katugma para sa pagsasaayos.

2. Ang EPF6016ATC144-2N ay angkop para sa maliit na produksyon na tumatakbo o prototyping?

Oo.Ang pakete ng TQFP-144 ay ginagawang madali sa prototype nang hindi nangangailangan ng mga advanced na tool sa pagpupulong.Mainam din ito para sa maliit na scale na produksyon kung saan kinakailangan ang mababang gastos at kakayahang umangkop.

3. Paano ihahambing ang EPF6016ATC144-2N sa mga mas bagong FPGA sa mga tuntunin ng pagganap?

Habang hindi bilang tampok na mayaman bilang modernong high-end na FPGA, ang EPF6016ATC144-2N ay nag-aalok ng maaasahang pagganap para sa katamtamang pagiging kumplikado ng lohika na may mas mababang pagkonsumo ng kuryente at mas simpleng pagsasama, na ginagawang epektibo ito para sa maraming mga aplikasyon.

4. Ligtas bang maiinit ang EPF6016ATC144-2N sa mga live system?

Oo.Sinusuportahan ng FPGA na ito ang hot-socketing para sa 3.3V system, na pinapayagan itong ipasok o alisin nang walang kapangyarihan sa host board, mainam para sa serbisyo sa patlang o mga disenyo ng hardware.

5. Bakit ko pipiliin ang EPF6016ATC144-2N sa mga pasadyang solusyon sa ASIC o CPLD?

Ang EPF6016ATC144-2N ay nag-aalok ng mas mabilis na pag-unlad ng mga siklo, in-field reprogramming, at nabawasan ang gastos sa itaas kumpara sa mga ASIC.Kung ikukumpara sa mga CPLD, nagbibigay ito ng mas maraming kapasidad ng lohika at nababaluktot na pagruruta, mainam para sa mga nasusukat at umuusbong na disenyo.

LC5768MC-75F256C CPLD: Mga tampok, specs, pakinabang at aplikasyon

sa 2025/07/10

Pagsisimula sa MC7447AHX1000NB

sa 2025/07/10

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/19 147781

-

USB-C pinout at mga tampok

sa 2000/04/19 112051

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/19 111352

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/19 83806

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79610

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66991

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63115

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63051

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54097

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52201