Latch vs Flip-Flop: Gabay sa Paghahambing para sa Digital Electronics

Ang mga latch at flip-flop ay mga pangunahing elemento ng digital storage na tumutulong sa iyong mag-imbak at makontrol ang binary data sa mga circuit.Sa artikulong ito, malalaman mo kung ano ang mga ito, kung paano gumagana ang mga ito, at kung paano naiiba ang kanilang pag-uugali sa oras.Tuklasin mo rin ang kanilang mga pakinabang, limitasyon, at karaniwang mga aplikasyon.Makakatulong ito sa iyong maunawaan kung kailan gagamitin ang bawat isa sa iyong mga disenyo.Catalog

Ano ang Latch sa Digital Electronics?

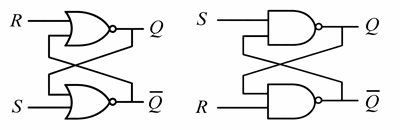

Figure 1. Basic Latch Circuit Diagram

Ang latch ay isang level-triggered na digital storage element na ginagamit upang mag-imbak ng isang bit ng binary data.Tumutugon ito sa isang enable o control signal na tumutukoy kung kailan maiimbak o mahawakan ang data.Ginagawa nitong mahalagang bahagi sa pangunahing digital electronics.Ang mga trangka ay karaniwang ipinapatupad gamit ang mga simpleng configuration ng gate ng lohika.Malawakang ginagamit ang mga ito sa mga circuit na nangangailangan ng pansamantalang pagpapanatili ng data.

Ang isang latch ay gumagana bilang isang pangunahing yunit ng memorya na maaaring mapanatili ang isang matatag na halaga ng output.Ang istraktura nito ay nagpapahintulot sa ito na humawak ng isang logic na estado hanggang ang isang kontrol na kundisyon ay nagpapahintulot ng isang update.Ginagawa nitong angkop para sa mga simpleng gawain sa pag-iimbak at pagkontrol sa mga digital system.Ang mga trangka ay kadalasang ginagamit bilang mga bloke ng gusali sa mas malalaking disenyo ng lohika.Ang kanilang pagiging simple ay ginagawa silang mahusay para sa mga low-complexity na circuit.

Ano ang Flip-Flop sa Digital Electronics?

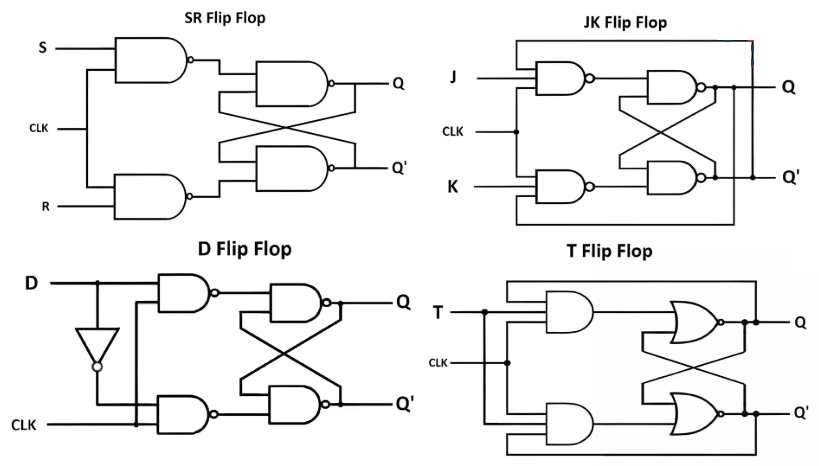

Figure 2. Basic Flip-Flop Circuit Diagram

Ang flip-flop ay isang edge-triggered digital storage element na nag-iimbak ng isang bit ng data bilang tugon sa isang signal ng orasan.Ito ay idinisenyo upang i-update ang estado nito lamang sa mga partikular na paglipat ng signal.Ang kinokontrol na pag-uugali na ito ay ginagawang mahalaga sa mga modernong digital system.Ang mga flip-flop ay malawakang ginagamit sa mga sequential logic circuit.Nagsisilbi ang mga ito bilang mga pangunahing bahagi sa maraming mga elektronikong disenyo.

Ang isang flip-flop ay gumaganap bilang isang maaasahang yunit ng memorya na nagpapanatili ng isang matatag na output sa pagitan ng mga kaganapan sa orasan.Tinitiyak ng disenyo nito na ang data ay nakaimbak sa isang kontrolado at predictable na paraan.Ang iba't ibang uri ng mga flip-flop ay sumusuporta sa iba't ibang logic function sa mga digital circuit.Ang mga aparatong ito ay karaniwang ginagamit bilang mga bloke ng gusali sa mga kumplikadong sistema.Ang kanilang nakaayos na pag-uugali ay ginagawa silang angkop para sa organisadong paghawak ng data.

Latch vs Flip-Flop Operation (Timing at Pagti-trigger)

Mga Pagbabago sa Latch State (Level-Triggered Operation)

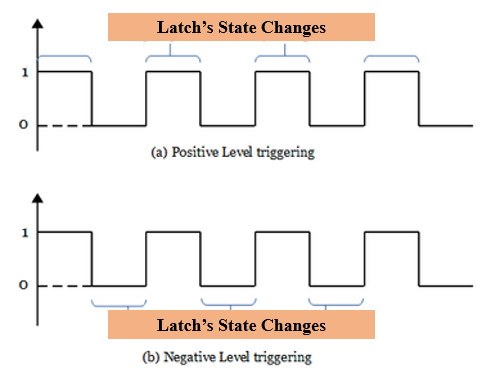

Figure 3. Latch Level-Triggered Timing Diagram

Ang latch ay patuloy na nagbabago ng estado habang ang enable signal ay nananatili sa isang aktibong antas, gaya ng inilalarawan ng mga naka-highlight na aktibong rehiyon sa waveform.Sa mga agwat na ito, direktang sinusundan ng output ang input, na nagpapahintulot sa mga update.Ang pag-uugali na ito ay makikita sa parehong positibo at negatibong antas ng pag-trigger, kung saan ang latch ay tumutugon batay sa kung ang control signal ay mataas o mababa.Kapag ang enable signal ay naging hindi aktibo, ang output ay hihinto sa pag-update at hawak ang huling naka-imbak na halaga.Ipinapakita ng waveform na maraming pagbabago sa input ang maaaring mangyari sa loob ng isang aktibong panahon, at lahat ay makikita sa output.Ang tuluy-tuloy na pagtugon na ito ay kilala bilang transparency sa level-triggered na operasyon.Bilang resulta, nakadepende ang gawi ng latch sa tagal ng signal sa halip na sa isang transition point.

Mga Pagbabago sa Estado ng Flip-Flop (Edge-Triggered Operation)

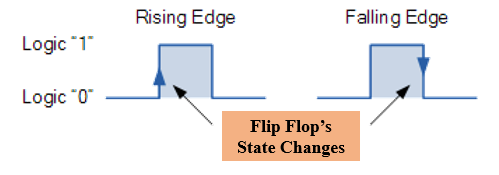

Figure 4. Flip-Flop Edge-Triggered Timing Diagram

Ang flip-flop ay nagbabago ng estado lamang sa mga partikular na transition point ng signal ng orasan, gaya ng ipinapahiwatig ng pagtaas at pagbaba ng mga gilid sa waveform.Eksaktong nag-a-update ang output sa mga gilid na ito, na kinukuha ang halaga ng input sa eksaktong sandaling iyon.Sa pagitan ng mga transition ng orasan, nananatiling hindi nagbabago ang output anuman ang mga variation ng input.Tinitiyak ng gawi na ito na ang mga pagbabago sa data ay magaganap lamang sa mahusay na tinukoy na mga instant.Itinatampok ng diagram kung paano kumikilos ang mga gilid ng transition bilang mga trigger point para sa mga update ng estado.Ang bawat gilid ay kumakatawan sa isang pagkakataon para sa flip-flop na mag-imbak ng bagong data.Ang edge-triggered mechanism na ito ay nagbibigay ng kontrolado at predictable na timing sa mga digital circuit.

Mga Kalamangan at Kahinaan ng Latch at Flip-Flop

Mga Bentahe ng Latch at Flip-Flop

• Nag-aalok ang mga latch ng mas mabilis na tugon dahil sa patuloy na pagsubaybay sa input.

• Ang mga latch ay gumagamit ng mas mababang kapangyarihan sa mga simpleng disenyo.

• Ang mga flip-flop ay nagbibigay ng tumpak na kontrol sa tiyempo na may pag-synchronize ng orasan.

• Binabawasan ng mga flip-flop ang panganib ng mga hindi sinasadyang pagbabago sa estado.

• Parehong sumusuporta sa maaasahang single-bit na imbakan ng data.

• Parehong mahalaga para sa pagbuo ng mga kumplikadong digital system.

Mga Limitasyon ng Latch at Flip-Flop

• Ang mga trangka ay sensitibo sa ingay sa panahon ng aktibong paggana.

• Ang mga trangka ay maaaring magdulot ng kawalan ng katiyakan sa timing sa mga kumplikadong sistema.

• Ang mga flip-flop ay nangangailangan ng higit pang circuitry, na nagdaragdag ng pagiging kumplikado.

• Ang mga flip-flop ay kumonsumo ng higit na lakas dahil sa paggamit ng orasan.

• Parehong nangangailangan ng maingat na disenyo ng timing upang maiwasan ang mga error.

• Parehong maaaring magpakilala ng pagkaantala ng pagpapalaganap sa mga circuit.

Mga Application ng Latches at Flip-Flops

1. Mga Rehistro ng Imbakan ng Data

Gumagamit ang mga register ng mga flip-flop upang mag-imbak ng maraming bit ng data sa mga processor at digital system.Pansamantala silang nagtataglay ng mga halaga sa panahon ng pag-compute at paglilipat ng data.Tinitiyak nito ang matatag na paghawak ng data sa pagitan ng mga yugto ng pagproseso.Ang mga rehistro ay mabuti para sa mga pagpapatakbo ng CPU, buffering, at pag-synchronize ng data.

2. Mga Counter at Timer

Ang mga flip-flop ay malawakang ginagamit upang bumuo ng mga digital na counter na sumusubaybay sa mga kaganapan o pulso ng orasan.Ang mga counter na ito ay mahusay sa timing circuits, frequency division, at digital clock.Pinapagana nila ang mga tumpak na pagpapatakbo ng pagbibilang sa mga naka-embed na system.Umaasa ang mga timer sa kanila upang kontrolin ang mga pagkaantala at mga pana-panahong pagkilos.

3. Mga Elemento ng Memorya sa Digital Circuits

Ang parehong mga latch at flip-flop ay nagsisilbing pangunahing mga yunit ng memorya sa digital electronics.Nag-iimbak sila ng binary data na maaaring ma-access o mabago kung kinakailangan.Ang function na ito ay kinakailangan para sa pagpapanatili ng estado ng system.Ang mga memory circuit ay umaasa sa mga elementong ito para sa matatag na operasyon.

4. Data Synchronization System

Nakakatulong ang mga flip-flop na i-synchronize ang mga signal sa iba't ibang domain ng orasan sa mga kumplikadong system.Tinitiyak nila na ang data ay inililipat nang walang mga error sa timing o glitches.Pinapabuti nito ang pagiging maaasahan ng system sa mga high-speed na disenyo.Mahalaga ang pag-synchronize sa mga unit ng komunikasyon at pagpoproseso.

5. Kontrolin ang Logic Circuits

Ang mga latch ay ginagamit sa mga control circuit kung saan kinakailangan ang agarang pagtugon sa mga pagbabago sa input.Tumutulong sila na pamahalaan ang mga signal, gating, at daloy ng lohika.Nagbibigay-daan ito sa kakayahang umangkop na kontrol sa mga digital na disenyo.Tinitiyak ng control logic ang wastong operasyon at pagkakasunud-sunod ng system.

6. Shift Registers

Ang mga flip-flop ay ginagamit upang bumuo ng mga shift register na naglilipat ng data nang sunud-sunod.Ginagamit ang mga ito sa serialization ng data, mga sistema ng komunikasyon, at pagproseso ng signal.Ang mga shift register ay nagbibigay-daan sa mahusay na paglipat ng data sa pagitan ng mga bahagi.Malawakang ginagamit ang mga ito sa mga interface ng digital na komunikasyon.

Pagkakaiba sa pagitan ng Flip-Flop at Latch

|

Aspeto |

Latch |

Flip-Flop |

|

Trigger

Mekanismo |

Sumasagot kapag

paganahin = HIGH o LOW (level-sensitive) |

Tumutugon lamang sa

gilid ng orasan (↑ o ↓) |

|

Control Signal

Uri |

Paganahin (EN)

hudyat |

Orasan (CLK)

hudyat |

|

Update ng Data

kundisyon |

Mga update

sa buong tagal ng aktibong antas |

Mga update nang isang beses bawat

gilid ng orasan |

|

Input Sampling

Bintana |

Buksan ang bintana

(batay sa tagal) |

Instant sampling

(batay sa gilid, ~ns range) |

|

Karaniwan

Pagkaantala ng Pagpapalaganap |

~1–5 ns (simple

pagkaantala ng gate) |

~5–20 ns

(kasama ang circuitry ng orasan) |

|

Circuit

Pagiging kumplikado |

4–6 na gate ng lohika

(pangunahing SR latch) |

10–20+ na gate

(edge-triggered na disenyo) |

|

kapangyarihan

Pagkonsumo |

Mas mababa (hindi

patuloy na paglipat ng orasan) |

Mas mataas (dahil sa

mga paglipat ng orasan) |

|

Lumipat

Limitasyon ng Dalas |

Limitado sa pamamagitan ng input

katatagan habang pinagana |

Maaaring mag-operate

maaasahan sa 100 MHz–GHz range |

|

glitch

pagiging sensitibo |

Mas mataas habang

aktibong panahon ng paganahin |

Mas mababa dahil sa

gilid paghihiwalay |

|

Timing Control

Katumpakan |

Depende sa

paganahin ang tagal ng signal |

Tinukoy ng

tumpak na mga gilid ng orasan |

|

Katatagan ng Data

(Hold Behaviour) |

Hinahawakan pagkatapos

nagiging hindi aktibo ang enable |

Hawak hanggang sa susunod

gilid ng orasan |

|

orasan

Kinakailangan |

Hindi kinakailangan |

Kinakailangan para sa

operasyon |

|

Angkop sa Estilo ng Disenyo |

Asynchronous o

simpleng control logic |

Kasabay

mga digital system |

|

Scalability sa

Mga sistema |

Hindi gaanong nasusukat

para sa malalaking disenyo |

Lubos na nasusukat

sa mga kumplikadong sistema |

|

Karaniwan

Paggamit ng Pagpapatupad |

Gating, simple

imbakan, mga landas ng kontrol |

Mga rehistro,

mga counter, pipeline |

Konklusyon

Ang mga latch at flip-flop ay parehong nagsisilbing mahalagang isang-bit na elemento ng imbakan ngunit naiiba pangunahin sa kung paano tumugon ang mga ito sa mga signal ng input at kontrol sa tiyempo.Ang mga latch ay nagbibigay ng mabilis, tuluy-tuloy na pagtugon sa pamamagitan ng level-triggered na operasyon, habang ang mga flip-flop ay nag-aalok ng tumpak at matatag na paghawak ng data sa pamamagitan ng edge-triggered na gawi.Ang bawat isa ay may sariling mga pakinabang at trade-off sa mga tuntunin ng kapangyarihan, pagiging kumplikado, at pagiging maaasahan.Ang pagpili sa pagitan ng mga ito ay depende sa mga kinakailangan sa timing, uri ng system, at pangkalahatang mga layunin sa disenyo sa digital electronics.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Ano ang pangunahing pagkakaiba sa pagitan ng kasabay at asynchronous na mga elemento ng imbakan?

Ang mga kasabay na elemento tulad ng mga flip-flop ay umaasa sa isang signal ng orasan, habang ang mga asynchronous na elemento tulad ng mga latch ay gumagana batay sa mga antas ng input na walang orasan.

2. Bakit mas pinipili ang mga flip-flop sa mga clocked digital system?

Tinitiyak ng mga flip-flop ang pagbabago ng data lamang sa tinukoy na mga gilid ng orasan, ginagawang predictable ang timing ng system at binabawasan ang mga error.

3. Maaari bang gawing flip-flop ang isang trangka?

Oo, ang pagsasama-sama ng dalawang latch sa isang master-slave na configuration ay maaaring lumikha ng isang flip-flop na may edge-triggered na gawi.

4. Ano ang mga karaniwang uri ng flip-flop na ginagamit sa mga digital circuit?

Kasama sa mga karaniwang uri ang SR, JK, D, at T na mga flip-flop, bawat isa ay idinisenyo para sa mga partikular na logic at control function.

5. Paano nakakaapekto ang mga isyu sa timing sa mga disenyong nakabatay sa latch?

Ang hindi tamang timing ay maaaring magdulot ng mga glitch o kundisyon ng lahi dahil ang mga latch ay nagbibigay-daan sa maraming pagbabago sa input sa mga panahon ng pag-enable.

Ipinaliwanag ang Cycloconverter: Simpleng Gabay sa Paggawa at Paggamit

sa 2026/04/3

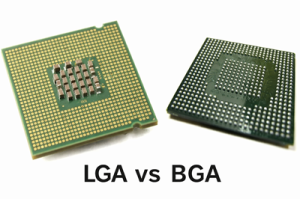

LGA vs BGA Comparison Guide para sa Electronic Systems Design

sa 2026/04/1

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147778

-

USB-C pinout at mga tampok

sa 2000/04/18 112033

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111352

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83792

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79596

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66976

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63110

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63043

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54097

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52197