Pangkalahatang-ideya ng EPM3256AQC208-10 Intel MAX 3000A Device

Makakakuha ka ng programmable logic device na tumutulong sa iyong pagsamahin ang maraming fixed logic function sa isang flexible chip.Hinahayaan ka ng EPM3256AQC208-10 na pamahalaan ang mga control path, timing signal, at mga interface nang hindi muling nagdidisenyo ng hardware sa tuwing kailangang magbago ang logic.Maaari mong i-update ang logic pagkatapos ng pag-install, na ginagawang mas madali ang mga pagsasaayos sa panahon ng pagsubok o paggamit sa ibang pagkakataon.Sa malinaw na istraktura, steady timing, at mataas na bilang ng pin, ang device na ito ay akma nang husto sa mga system na nangangailangan ng maaasahang digital na kontrol nang walang kumplikado ng mas malalaking programmable platform.Catalog

Pangkalahatang-ideya ng EPM3256AQC208-10

Ang EPM3256AQC208-10 ay isang programmable logic device na idinisenyo upang pangasiwaan ang mid-level na digital na kontrol at mga gawain sa interface sa loob ng isang bahagi.Pinagsasama nito ang mga mapagkukunan ng lohika na maaaring i-configure na may mahuhulaan na gawi sa timing, na nagpapahintulot sa maramihang mga fixed logic function na pagsama-samahin sa isang flexible na disenyo.Sinusuportahan ng device ang mga update pagkatapos ng pag-install, na tumutulong sa pagtanggap ng mga pagbabago sa disenyo nang walang pagpapalit ng hardware.Ito ay karaniwang ginagamit sa mga control circuit, interface adaptation, address decoding, at simpleng sequencing function.Pinapaboran ng istraktura nito ang matatag na paghawak ng signal at pare-parehong pagtugon, na ginagawang angkop para sa mga system na umaasa sa mga tinukoy na landas ng lohika kaysa sa pagproseso ng mataas na density.Naghahanap ng EPM3256AQC208-10?Makipag-ugnayan sa amin upang suriin ang kasalukuyang stock, oras ng pag-lead, at pagpepresyo.

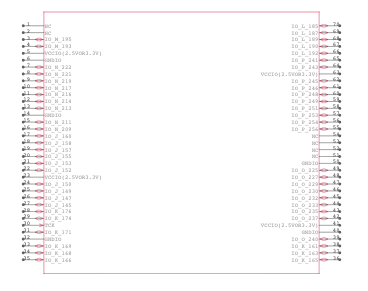

Pin-Out Diagram ng EPM3256AQC208-10

[LARAWAN NG 208–Pin PQFP Package Pin-Out Diagram]

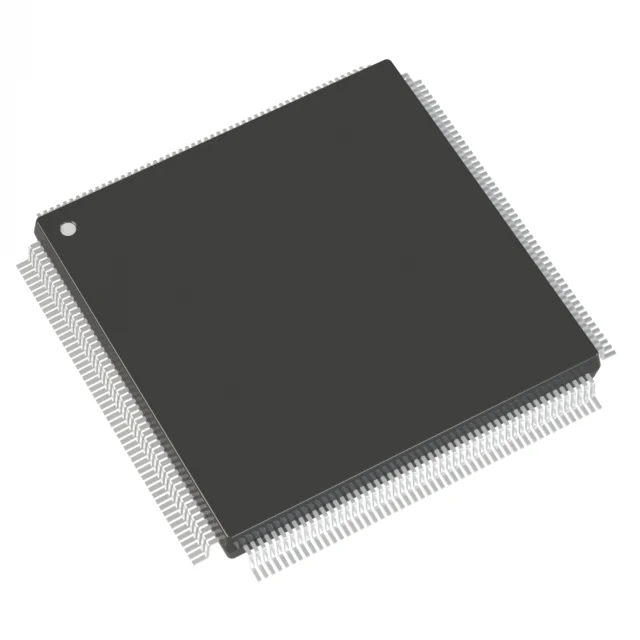

Ang layout ng square package ay tumutukoy sa pisikal na pin arrangement para sa 208 pin plastic quad flat pack na ginagamit ng device, na may mga pin na ipinamahagi nang pantay-pantay sa lahat ng apat na gilid.Ang Pin 1 ay minarkahan sa kaliwang sulok sa itaas, at ang pagnunumero ay nagpapatuloy nang sunud-sunod sa paligid ng perimeter ng package, na may mga reference point na ipinapakita sa mga pin 53, 105, at 157 upang ipahiwatig ang mga side transition.Natukoy ang balangkas ng package bilang hindi iginuhit sa sukat, na nagbibigay-diin sa oryentasyon at pagnunumero sa halip na mga sukat.Tinutukoy ng gitnang pag-label ang mga katugmang variant ng device, habang sinusuportahan ng simetriko na istraktura ng lead ang mataas na pin count connectivity para sa power, ground, at user I O signal.

EPM3256AQC208-10 CAD na Modelo

EPM3256AQC208-10 Simbolo

EPM3256AQC208-10 Bakas ng paa

EPM3256AQC208-10 3D na Modelo

Mga tampok ng EPM3256AQC208-10

MAX 3000A CPLD Family Membership

Ang device ay bahagi ng MAX 3000A CPLD family, na idinisenyo para sa stable na digital logic control at mga gawain sa interface.Nakatuon ang pamilyang ito sa predictable na gawi at paulit-ulit na timing, na ginagawa itong angkop para sa mga system na nangangailangan ng pare-parehong logic operation.Nagbibigay-daan ito sa maramihang mga fixed logic function na pagsamahin sa isang configurable device, na binabawasan ang pagiging kumplikado ng circuit.

In-System Programmable Architecture

Ang EPM3256AQC208-10 ay sumusuporta sa in-system programming, na nagbibigay-daan sa mga logic configuration na maisulat, ma-update, o maitama pagkatapos mai-install ang device sa isang circuit board.Sinusuportahan ng kakayahang ito ang mga pagbabago sa disenyo nang walang pagpapalit ng hardware at pinapasimple ang mga update sa panahon ng pag-develop o pagpapanatili.Nakakatulong din itong bawasan ang downtime kapag kailangan ang mga pagsasaayos ng lohika.

Mabilis na Pagganap ng Pagkaantala ng Propagation

Nag-aalok ang device ng maximum na pagkaantala ng propagation na 10 ns, na nagbibigay-daan sa mabilis na pagtugon sa pagitan ng mga logic input at output.Sinusuportahan nito ang mga application na umaasa sa napapanahong mga transition ng signal at kinokontrol na mga path ng pagtugon.Ang pare-parehong gawi sa pagkaantala ay nakakatulong na mapanatili ang maaasahang operasyon sa magkasabay at nakabatay sa kontrol na mga disenyo.

Panloob na Operating Voltage Range

Gumagana ang panloob na lohika sa loob ng saklaw ng boltahe na 3.0 V hanggang 3.6 V, na umaayon sa mga karaniwang low-voltage na digital system.Sinusuportahan ng hanay na ito ang matatag na operasyon ng logic habang pinapanatili ang pagiging tugma sa mga nakapaligid na bahagi.Nakakatulong din itong pamahalaan ang pag-uugali ng kapangyarihan sa mga compact na digital na disenyo.

Macrocell-Based Logic Resources

May kabuuang 256 macrocells ang available para ipatupad ang mga programmable logic function.Sinusuportahan ng mga macrocell na ito ang combinational at rehistradong logic, na nagbibigay-daan sa flexible na pagpapatupad ng control logic at mga function ng interface.Ang kapasidad na ito ay nababagay sa mga kinakailangan sa mid-level na logic nang walang overhead ng mas malalaking programmable device.

Organisadong Logic Block Structure

Ang panloob na arkitektura ay nakaayos sa 16 na bloke ng lohika, na nagbibigay ng isang nakabalangkas na diskarte sa paglalagay ng lohika at daloy ng signal.Tumutulong ang organisasyong ito na mapanatili ang predictable na timing at pinapasimple ang pamamahala ng mga logic path.Sinusuportahan nito ang maayos na pagpapatupad ng disenyo para sa control at sequencing na mga gawain.

Nagagamit na Logic Gate Capacity

Nagbibigay ang device ng humigit-kumulang 5000 na magagamit na logic gate, na nagbibigay-daan dito na palitan ang ilang discrete logic component sa loob ng isang pakete.Nakakatulong ang pagsasama-samang ito na bawasan ang espasyo ng board at pinapasimple ang layout ng system.Ito ay angkop para sa mga disenyo na nangangailangan ng katamtamang pagiging kumplikado ng lohika.

Mataas na User Input Output Availability

Kasama sa EPM3256AQC208-10 ang 158 input at output pin ng user, na nagbibigay-daan sa malawak na koneksyon sa mga panlabas na signal at device.Sinusuportahan ng mataas na bilang ng pin na ito ang mga kumplikadong pangangailangan sa interfacing gaya ng pag-decode ng address, kontrol ng bus, at pagruruta ng signal.Nagbibigay-daan ito sa nababaluktot na pagsasama sa loob ng mas malalaking digital system.

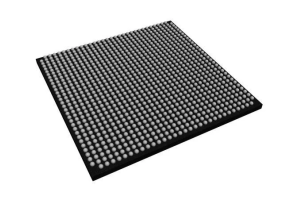

Surface Mount PQFP Package

Nakalagay ang device sa isang 208 pin PQFP surface mount package na idinisenyo para sa mga siksik na layout ng circuit board.Sinusuportahan ng package na ito ang maaasahang mga de-koryenteng koneksyon habang umaangkop sa s

EPM3256AQC208-10 Mga Teknikal na Pagtutukoy

| Katangian ng Produkto | Halaga ng Katangian |

| Manufacturer | Intel |

| Supply ng Boltahe - Panloob | 3V ~ 3.6V |

| Package ng Supplier ng Device | 208-PQFP (28x28) |

| Serye | MAX® 3000A |

| Uri ng Programmable | Sa System Programmable |

| Package / Case | 208-BFQFP |

| Package | Tray |

| Operating Temperatura | 0°C ~ 70°C (TA) |

| Bilang ng Macrocells | 256 |

| Bilang ng Logic Elements/Blocks | 16 |

| Bilang ng I/O | 158 |

| Bilang ng Gates | 5000 |

| Uri ng Pag-mount | Ibabaw na Mount |

| Oras ng Pagkaantala tpd(1) Max | 10 ns |

| Batayang Numero ng Produkto | EPM3256 |

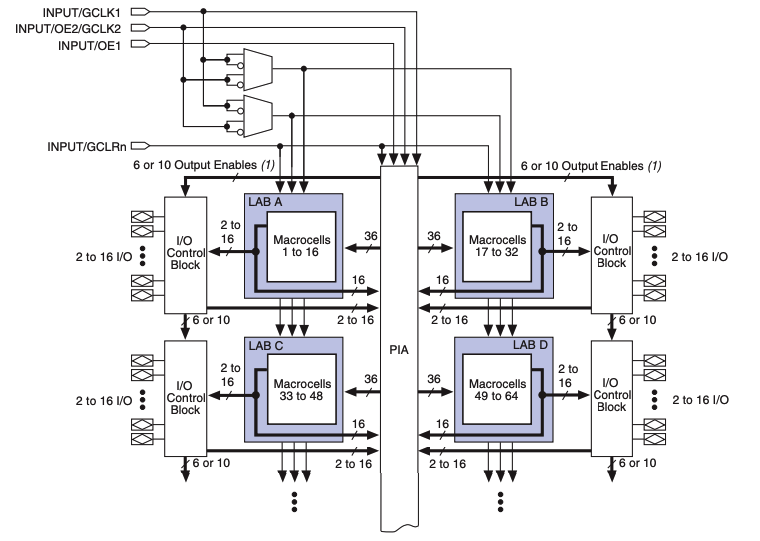

Block Diagram ng Device ng EPM3256AQC208-10

Ang panloob na arkitektura ay nakaayos sa paligid ng maramihang Logic Array Blocks na may label na A hanggang D, bawat isa ay naglalaman ng mga grupo ng mga macrocell na ginagamit upang ipatupad ang mga programmable logic function.Ang mga Macrocell ay konektado sa pamamagitan ng isang gitnang Programmable Interconnect Array na nagbibigay ng mga routing path sa pagitan ng mga logic block at namamahagi ng mga signal sa buong device.Ang I/O Control Blocks ay nakaposisyon sa paligid ng logic array at pinamamahalaan ang daloy ng data sa pagitan ng panloob na logic at panlabas na mga pin, na sumusuporta sa maaaring i-configure na input, output, at bidirectional na operasyon.Ang mga pandaigdigang linya ng kontrol sa pamamahagi ng orasan sa tuktok na hawakan, ang kontrol sa pag-enable ng output, at mga pandaigdigang malinaw na pag-andar, na nagbibigay-daan sa naka-synchronize na operasyon sa lahat ng bloke ng lohika.Isinasaad ng mga annotation sa lapad ng signal ang bilang ng magagamit na pagruruta at paganahin ang mga linya sa pagitan ng mga bloke, na sumasalamin sa naayos at nahuhulaang istraktura na ginagamit sa buong MAX 3000A na pamilya.

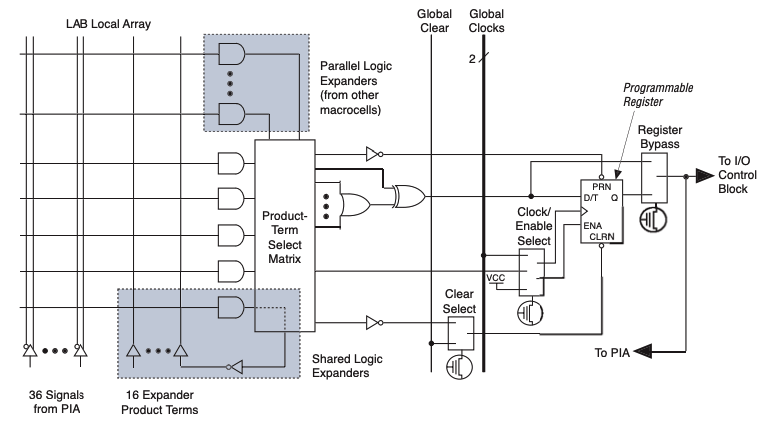

Macrocell ng EPM3256AQC208-10

Pinagsasama ng istruktura ng Macrocell ang isang termino ng produkto na piliin ang matrix na may parallel at shared logic expander upang bumuo ng nako-configure na combinational logic sa loob ng Logic Array Block.Dumarating ang mga signal ng input mula sa Programmable Interconnect Array at lokal na pagruruta ng LAB, na nagpapakain ng hanggang labing-anim na termino ng produkto na pinagsama-sama sa pamamagitan ng mga napiling logic path.Ang output ay maaaring i-ruta nang direkta o sa pamamagitan ng isang programmable register na kinabibilangan ng clock enable, clear control, at access sa global clock at global clear signal.Ang isang register bypass path ay nagbibigay-daan sa puro kumbinasyonal na operasyon, habang ang kinokontrol na feedback ay nagruruta ng resulta pabalik sa interconnect array o patungo sa I/O control block para sa panlabas na koneksyon.

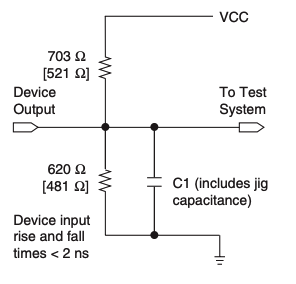

Mga Kondisyon ng Pagsubok sa AC ng EPM3256AQC208-10

Tinutukoy ng configuration ng pagsubok ang panlabas na circuit na ginagamit upang sukatin ang pagganap ng AC ng mga daanan ng input at output ng device sa ilalim ng mga kontroladong kundisyon.Ang isang resistive network ay nagkokonekta sa output ng device sa supply at lupa gamit ang mga tinukoy na halaga ng risistor na naiiba para sa 2.5 V at 3.3 V na operasyon, na nagtatatag ng mga kilalang katangian ng pagkarga.Ang isang kapasitor na nakakonekta sa lupa ay kumakatawan sa kabuuang kapasidad ng pagkarga, kabilang ang mga epekto ng kabit ng pagsubok, habang ang node ng pagsukat ay nakikipag-ugnayan sa sistema ng pagsubok.Pinipigilan ng setup ang mga oras ng pagtaas at pagbaba ng input sa mas mababa sa dalawang nanosecond at pinapaliit ang ingay na dulot ng ground current transients sa panahon ng pagpapalit ng output, na tinitiyak ang pare-pareho at nauulit na mga resulta ng timing ng AC.

Mga aplikasyon ng EPM3256AQC208-10

Pagpapalit ng Pandikit na Logic para sa Mga Discrete na Bahagi

Ang EPM3256AQC208-10 ay karaniwang ginagamit upang palitan ang mga koleksyon ng mga fixed logic device gaya ng mga gate, decoder, at multiplexer.Sa pamamagitan ng pagsasama-sama ng mga function na ito sa isang programmable device, nagiging mas simple at mas madaling pamahalaan ang mga layout ng system.Ang lohika na pag-uugali ay maaari ding ayusin sa pamamagitan ng reprogramming, na sumusuporta sa pagpipino ng disenyo nang walang mga pagbabago sa hardware.

Decoding at Kontrol ng Address sa Mga Naka-embed na System

Sa mga naka-embed na system, pinangangasiwaan ng device ang pag-decode ng address at kontrolin ang mga gawain na nag-uugnay sa memorya, peripheral, at control signal.Tinutulungan nito ang direktang daloy ng data at pamahalaan ang mga signal na paganahin nang may pare-parehong timing.Ginagawa nitong angkop para sa mga system na umaasa sa malinaw na paghihiwalay ng mga puwang ng address at predictable control behavior.

Bus Interfacing at Protocol Adaptation

Inilapat ang device sa mga tungkulin sa interfacing ng bus kung saan dapat gumana nang magkasama ang iba't ibang format ng signal o mga kinakailangan sa timing.Sinusuportahan nito ang signal conditioning, routing, at basic protocol translation sa pagitan ng mga subsystem.Nakakatulong ito na mapanatili ang maayos na mga landas ng komunikasyon sa loob ng halo-halong o legacy na mga digital na kapaligiran.

Mga Industrial Control Panel at Automation Equipment

Sa loob ng mga pang-industriyang control panel, pinamamahalaan ng EPM3256AQC208-10 ang sequencing, interlock logic, at status monitoring.Sinusuportahan ng stable timing nito ang coordinated operation ng mga sensor, actuator, at control signal.Tamang-tama ang device sa automation equipment na pinahahalagahan ang maaasahang operasyon ng logic kaysa sa mataas na kumplikado sa pagproseso.

Telecommunications Support Logic Functions

Ang aparato ay nagsisilbing pansuportang lohika sa mga sistema ng telekomunikasyon, paghawak ng kontrol sa tiyempo, koordinasyon ng interface, at mga pantulong na digital function.Nakakatulong itong ayusin ang mga ugnayan ng signal sa pagitan ng mga functional block.Sinusuportahan ng papel na ito ang pare-parehong operasyon sa mga kagamitan sa komunikasyon na nakadepende sa maayos na digital na kontrol.

Kontrol at Timing ng Consumer Electronics

Sa consumer electronics, ginagamit ang device para sa control at timing function gaya ng input handling, mode selection, at system coordination.Ang pagiging programmable nito ay nagpapahintulot sa isang disenyo na suportahan ang maramihang mga variation ng produkto.Sinusuportahan ng flexibility na ito ang mga compact at adaptable na consumer device.

Pagpapanatili at Muling Disenyo ng Legacy System

Ang EPM3256AQC208-10 ay angkop para sa pagpapanatili o pag-update ng mga legacy system na nangangailangan ng pin-compatible na programmable logic.Pinapayagan nito ang mga umiiral na layout ng hardware na manatiling hindi nagbabago habang ang lohika na pag-uugali ay binago.Nakakatulong ang diskarteng ito na palawigin ang buhay ng system habang pinapanatili ang pagsusumikap sa muling pagdidisenyo na mapapamahalaan.

EPM3256AQC208-10 Mga Kalamangan at Kahinaan

Mga kalamangan

• Sinusuportahan ng in-system programmability ang mga update sa logic nang hindi inaalis ang device

• Ang maximum na 10 ns delay ay nagbibigay-daan sa tumutugon na digital signal handling

• Ang mataas na bilang ng mga I O pin ay sumusuporta sa malawak na panlabas na koneksyon

• Sinusuportahan ng nahuhulaang gawi sa timing ang matatag na operasyon ng lohika ng kontrol

• Angkop para sa pandikit na lohika, mga function ng kontrol, at pag-bridging ng interface

• Sinusuportahan ng PQFP package ang mas madaling inspeksyon at pagpupulong kumpara sa mga array package

Mga disadvantages

• Limitadong mapagkukunan ng lohika kumpara sa mga mas bagong programmable logic device

• Ang operasyon ay limitado sa isang komersyal na hanay ng temperatura mula 0 C hanggang 70 C

• Mas mataas na paggamit ng kuryente kaysa sa mas kamakailang mga low-power na solusyon sa lohika

• Mas malaking package footprint kumpara sa mga modernong compact na alternatibo

• Mas kaunting feature ng integration kaysa sa mga advanced na programmable platform

EPM3256AQC208-10 Mga Alternatibo

| Numero ng Bahagi | Manufacturer | Mga Pangunahing Tampok | Gamitin ang Case/Notes |

| EPM3256AQI208-10 | Intel | Miyembro ng MAX 3000A CPLD family na may 256 macrocells, in-system programmability, at stable na 3 V na operasyon para sa maaasahang kontrol ng logic. | Ginagamit sa mga pang-industriya at naka-embed na system para sa pandikit na lohika, kontrol sa interface, at katamtamang bilis na mga digital na disenyo. |

| EPM3256AQI208-10N | Intel | Parehong logic density at arkitektura tulad ng iba pang mga EPM3256 device, na may predictable timing at flexible I/O handling. | Angkop para sa mga legacy na disenyo at naka-embed na platform na nangangailangan ng maaasahang CPLD-based logic integration. |

| EPM3256AQC208-7N | Intel | Mas mabilis na bilis-grade variant na nag-aalok ng mas mababang propagation delay habang pinapanatili ang parehong macrocell at I/O structure. | Tamang-tama para sa timing-sensitive logic gaya ng bus arbitration, state machines, at performance-critical control paths. |

Tungkol sa Intel

Ang Intel ay isang pandaigdigang kumpanya ng teknolohiya na kilala sa pagbuo ng malawak na hanay ng digital computing at programmable logic na produkto.Ang portfolio nito ay sumasaklaw sa mga processor, programmable device, at system solutions na ginagamit sa computing, komunikasyon, at industriyal na merkado.Ang kumpanya ay may mahabang kasaysayan ng pagsulong ng mga digital na tool sa disenyo at mga platform na sumusuporta sa maaasahang pagbuo ng system.Sa pamamagitan ng patuloy na pamumuhunan sa teknolohiya ng proseso at pagsasama-sama ng produkto, sinusuportahan ng Intel ang mga nasusukat na solusyon na nagsisilbi sa parehong mga naka-embed na system at mga application na may mataas na pagganap.Ang mga pamilya ng produkto nito ay malawakang pinagtibay sa mga system na nagpapahalaga sa pagkakapare-pareho, pangmatagalang suporta, at malawak na pagkakatugma ng ekosistema.

Konklusyon

Nag-aalok ang EPM3256AQC208-10 ng malinaw na paraan para pangasiwaan ang mid-level na digital logic sa isang device.Maaari mong palitan ang mga grupo ng mga fixed logic na bahagi habang pinapanatili ang pag-uugali ng timing na matatag at madaling hulaan.Ang disenyong nakabatay sa macrocell nito ay nagbibigay sa iyo ng sapat na puwang para sa kontrol, pag-decode, at mga gawain sa interface.Sinusuportahan din ng 208-pin na pakete ang malawak na pag-access ng signal kapag mahalaga ang mga koneksyon.Sa in-system programming, maaari mong ayusin ang logic nang hindi hinahawakan ang board.Sa pangkalahatan, binibigyan ka nito ng praktikal na balanse ng flexibility at istraktura para sa pangmatagalang paggamit.

Datasheet PDF

EPM3256AQC208-10 Datasheet:

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Anong uri ng device ang EPM3256AQC208-10?

Ito ay isang CPLD na pinagsasama ang mga programmable logic function sa isang solong chip para sa kontrol at mga gawain sa interface.

2. Maaari bang i-reprogram ang EPM3256AQC208-10 pagkatapos ng pag-install?

Oo, sinusuportahan nito ang in-system programming, para ma-update mo ang logic habang nasa board na ito.

3. Ilang macrocells mayroon ang EPM3256AQC208-10?

Kasama sa device ang 256 macrocells para sa pagbuo ng combinational at rehistradong logic.

4. Anong pakete ang ginagamit para sa EPM3256AQC208-10?

Ito ay nasa isang 208-pin na PQFP surface-mount package.

5. Saan karaniwang ginagamit ang EPM3256AQC208-10?

Madalas itong ginagamit para sa lohika ng pandikit, pag-decode ng address, kontrol ng bus, at pangkalahatang mga function ng digital control.

Understanding Film Capacitors for Everyday Circuits

sa 2025/12/18

EP2S60F1020I4 Device Guide para sa Logic, Memory, at I/O

sa 2025/12/18

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147764

-

USB-C pinout at mga tampok

sa 2000/04/18 111987

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111351

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83751

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79542

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66949

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63089

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63028

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54092

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52172