XCV200-6FG456C FPGA: Mga tampok, pagtutukoy, programming, at mga aplikasyon

Ang XCV200-6FG456C ay isang malakas na FPGA (larangan ng gate-programmable gate) mula sa serye ng AMD Xilinx Virtex®.Ipinapaliwanag ng gabay na ito ang mga tampok nito, layout ng pin, mga hakbang sa pagprograma, at paggamit.Sa pamamagitan ng mataas na lakas ng pagproseso, nababaluktot na mga pagpipilian sa disenyo, at malakas na pag -input/output (I/O) na kakayahan, ang FPGA na ito ay tumutulong na bumuo ng mabilis at maaasahang mga digital system.Kung nagtatrabaho ka sa networking, control system, o pasadyang electronics, tutulungan ka ng gabay na ito na maunawaan kung paano maaaring magamit ang XCV200-6FG456C sa iyong mga proyekto.Catalog

XCV200-6FG456C Pangkalahatang-ideya

Ang XCV200-6FG456C ay isang kilalang modelo sa loob ng pamilyang AMD Xilinx Virtex® FPGA, na idinisenyo upang magbigay ng matatag na mga solusyon sa lohika na ma -program para sa mga kumplikadong digital system.Ang tiyak na chip na ito ay sumasaklaw sa humigit -kumulang na 236,666 system gate at nagtatampok ng 1,176 na -configure na mga bloke ng lohika (CLB) at 5,292 logic cells.Kasama rin dito ang 57,344 kabuuang mga bits ng RAM at sumusuporta sa 284 I/O pin, na nakalagay sa isang 456-ball fine-pitch ball grid array (FBGA) package, na may sukat na 23mm x 23mm.Ang modelong ito ay nagpapatakbo sa isang 2.5V nominal boltahe, na may saklaw na 2.375V hanggang 2.625V, at maaaring gumana sa loob ng isang saklaw ng temperatura na 0 ° C hanggang 85 ° C.Ang mas malawak na serye ng Virtex® ay tumutugma sa isang hanay ng mga aplikasyon na may mga density mula sa 50,000 hanggang sa higit sa 1 milyong mga pintuan ng system at mga rate ng orasan ng system na hanggang sa 200 MHz.Sinusuportahan nito ang maraming mga pamantayan sa I/O kabilang ang LVTTL, LVCMOS, at PCI, bukod sa iba pa.Ang mga tampok tulad ng pagkaantala na naka-lock na mga loop (DLL), mai-configure na mga bloke ng lohika na may naka-embed na memorya, at dedikadong pagdala ng lohika para sa mga operasyon ng aritmetika ay nagpapaganda ng pag-andar nito.Ginawa gamit ang isang 0.22 µM 5-layer na proseso ng metal, ginagarantiyahan ng pamilya ng Virtex® ang pagganap at pagiging maaasahan.

Kung nais mong isama ang top-tier na teknolohiya ng FPGA sa iyong mga produkto o system, ang pagbili ng XCV200-6FG456C na malaki sa amin ay isang matalinong paglipat.Natugunan nito ang mga pamantayan sa industriya at pinapanatili ka nang maaga sa mga pangangailangan sa teknolohiya sa hinaharap.

Mga tampok na XCV200-6FG456C

At Mga Gates ng System: Ang XCV200-6FG456C ay nag-aalok ng humigit-kumulang na 236,666 system gate.Ang mataas na bilang ng gate na ito ay nagbibigay -daan para sa pagpapatupad ng kumplikadong integrated digital logic circuit sa isang solong chip, pagpapahusay ng parehong pagganap at kakayahang magamit sa isang hanay ng mga aplikasyon.

At Mga mapagkukunan ng lohika: Kasama dito ang 1,176 na -configure na mga bloke ng lohika (CLB) at 5,292 mga cell ng lohika.Ang mga mapagkukunang ito ay mabuti para sa pagdidisenyo ng nababaluktot at nasusukat na mga digital na circuit.Ang mga CLB ay maaaring ma -program upang maisagawa ang isang iba't ibang mga lohikal na pag -andar, habang ang malaking bilang ng mga lohika cells ay nagbibigay -daan sa paghawak ng malawak na mga operasyon at proseso ng lohika.

At Memorya: Ang aparato ay nagbibigay ng 57,344 bits ng RAM, na ipinamamahagi sa mga bloke ng lohika.Ang naka-embed na RAM na ito ay ginagamit para sa mga application na nangangailangan ng mabilis at mahusay na pag-iimbak ng data at pagkuha, na sumusuporta sa mga operasyon ng data ng high-speed na integral sa mga modernong digital system.

At Mga Kakayahang I/O.: Sa 284 input/output pin, ang XCV200-6FG456C ay nagpapadali ng malawak na mga kakayahan sa pakikipag-ugnay.Ang mga I/O pin na ito ay sumusuporta sa iba't ibang mga pamantayan ng signal at paganahin ang FPGA na makipag -usap nang epektibo sa iba pang mga sangkap sa isang sistema, tulad ng mga aparato ng memorya, mga processors, at peripheral.

At Boltahe at saklaw ng temperatura: Ang pagpapatakbo sa isang nominal na boltahe ng 2.5V, na may katanggap-tanggap na saklaw mula sa 2.375V hanggang 2.625V, ang FPGA na ito ay idinisenyo para sa pagkonsumo ng mababang kapangyarihan habang pinapanatili ang matatag na pagganap.Maaari itong gumana sa loob ng isang saklaw ng temperatura ng kantong na 0 ° C hanggang 85 ° C, tinitiyak ang pagiging maaasahan sa ilalim ng iba't ibang mga kondisyon sa kapaligiran.

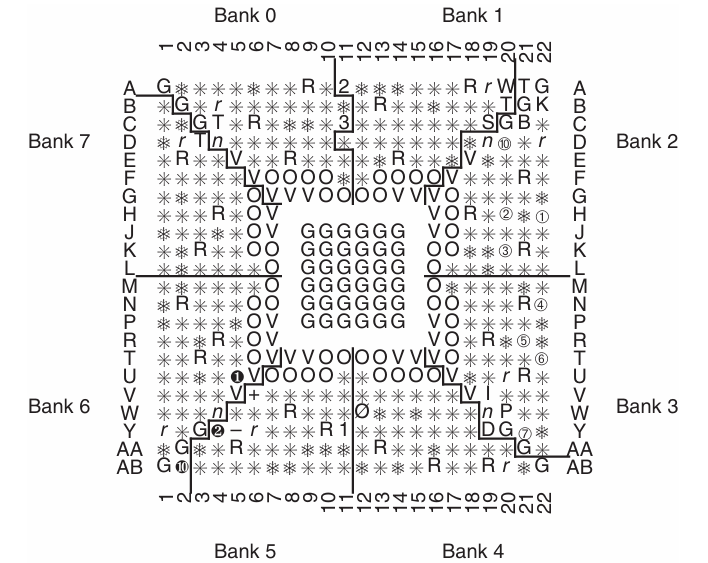

XCV200-6FG456C PIN function diagram

Ang XCV200-6FG456C PIN function diagram ay isang nakabalangkas na representasyon ng mga takdang pin ng FPGA, na ikinategorya sa iba't ibang mga bangko (Bank 0 hanggang Bank 7).Ang bawat grupo ng bangko ay batay sa kanilang pag -andar at pisikal na paglalagay sa package ng FPGA.Ang sistema ng pag -numero at pag -label ay sumusunod sa isang pattern ng grid kung saan ang mga hilera ay tinutukoy ng mga titik (A, B, C, atbp.), At mga haligi sa pamamagitan ng mga numero (1, 2, 3, atbp.), Na nagpapadali ng mabilis na pagkakakilanlan ng mga tiyak na pin.Ang mga bangko na ito ay tumutugma sa iba't ibang mga pag -andar ng input/output, kapangyarihan, lupa, at nakatuon na pag -ruta ng signal.Ang mga pin ay itinalaga ng iba't ibang mga functional na pangkat, kabilang ang pangkalahatang layunin I/O (GPIO), na madalas na may label na "G" (pangkalahatang input/output), "V" (supply ng boltahe), at "O" (output).Ang mga pin at ground pin ay minarkahan nang malinaw, tinitiyak ang matatag na operasyon ng FPGA.Ang mga espesyal na layunin na pin tulad ng mga pag-input ng orasan, pag-reset, at mga signal ng kontrol ay nakilala na may mga simbolo tulad ng "R" o "T."Ang ilang mga pin ay naghahain din ng mga nakatuong tungkulin sa komunikasyon, kabilang ang pagsasaayos ng JTAG at high-speed orasan, para sa programming at debugging.

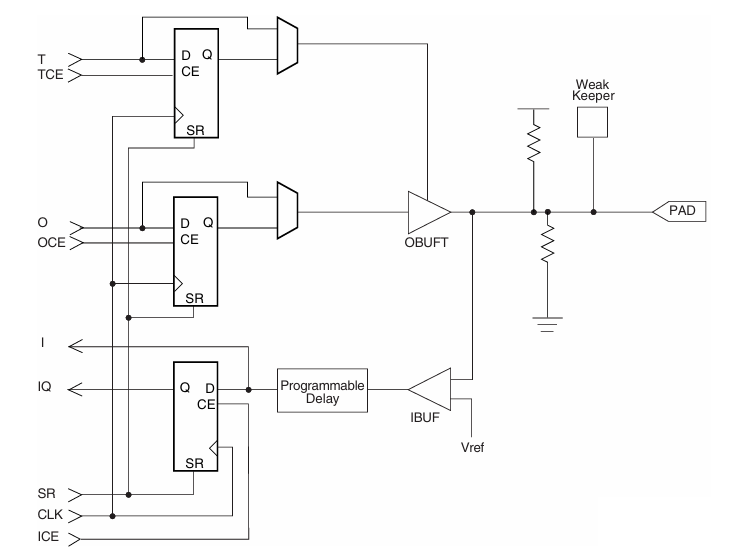

XCV200-6FG456C block diagram

INPUT/OUTPUT BLOCK

Ang diagram ay kumakatawan sa Input/Output Block (IOB) Istraktura ng XCV200-6FG456C FPGA, na isang miyembro ng pamilyang Xilinx Virtex.Ang diagram ay nagpapakita ng mga pangunahing elemento na kasangkot sa mga operasyon ng input at output, na nagtatampok ng mga mekanismo ng daloy ng data at kontrol.Sa core ng diagram, ang tatlong D flip-flops ay ginagamit upang magrehistro ng mga signal para sa input, output, at tri-state control.Ang output rehistro ay kinokontrol ng OCE (Output Clock Paganahin) signal, na tumutukoy kung kailan ang data ng output ay latched.Katulad nito, ang rehistro ng TRI-STATE ay kinokontrol ng TCE (tri-state clock na paganahin), pagpapagana o paganahin ang output buffer.Kinukuha ng Input Register ang papasok na data at nalalapat ang isang na -program na pagkaantala bago maipasa ito sa panloob na logic ng FPGA sa pamamagitan ng IBUF (input buffer).Ang Obuft (Tri-State Output Buffer) ay nagsisiguro na ang FPGA ay maaaring magmaneho ng isang signal papunta sa PAD (I/O PIN) o ilagay ito sa isang estado ng mataas na impedance, depende sa control logic.Ang isang mahina na circuit ng tagabantay ay kasama sa pad upang mapanatili ang huling kilalang estado ng lohika kapag walang aktibong driver na naroroon, na pumipigil sa hindi sinasadyang lumulutang na mga kondisyon.Ang sangguniang boltahe (VREF) ay ginagamit para sa ilang mga pamantayan sa pag -input, tulad ng SSTL o HSTL, na nangangailangan ng tumpak na mga antas ng boltahe para sa wastong operasyon.Sa pangkalahatan, ang istraktura ng IOB na ito ay nagbibigay-daan sa FPGA na pamahalaan ang paghahatid ng data ng high-speed, suportahan ang iba't ibang mga pamantayan sa I/O, at magbigay ng kakayahang umangkop na kontrol sa tiyempo at integridad ng signal.

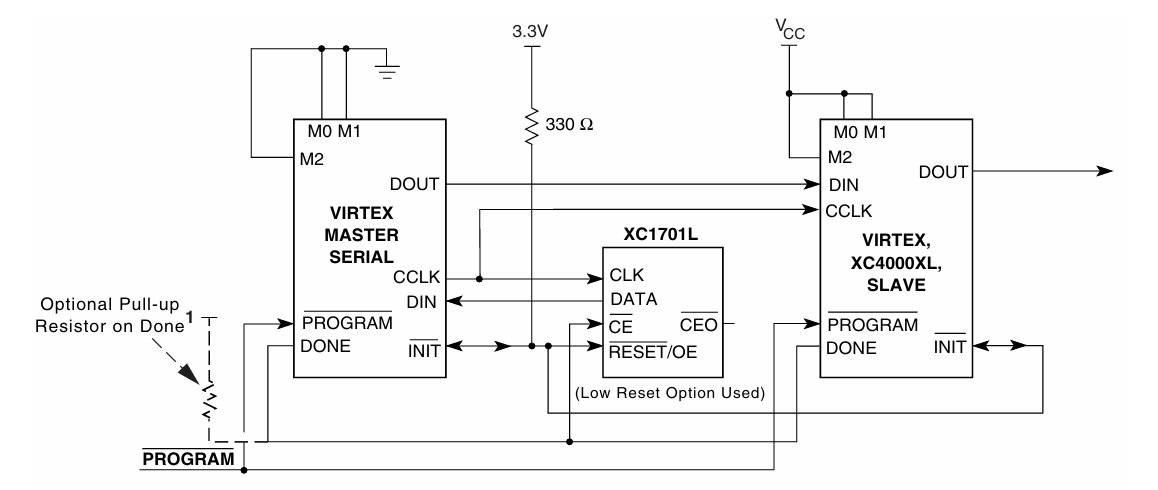

Master/Slave Serial Mode

Ang Master/Slave Serial Mode Inilalarawan ng block diagram ang proseso ng pagsasaayos ng isang Virtex FPGA, partikular ang XCV200-6FG456C, kapag na-program sa isang pagsasaayos ng daisy-chain gamit ang isang serial EEPROM (XC1701L).Sa pag -setup na ito, ang isang aparato ng Virtex ay nagpapatakbo bilang master, na kinokontrol ang pagsasaayos ng orasan (CCLK) at serially transmitting data ng pagsasaayos sa karagdagang mga FPGA ng alipin sa chain.Sinimulan ng Master FPGA ang proseso ng pagsasaayos sa pamamagitan ng pagsasaalang -alang sa signal ng programa, na -reset ang lahat ng mga aparato sa kadena.Kapag kumpleto ang pagsisimula, ang signal ng init ay nagpapahiwatig ng pagiging handa, at ang data ng pagsasaayos ay dumadaloy mula sa serial EEPROM (XC1701L) hanggang sa DIN (Data in) pin ng master FPGA.Ang Master FPGA ay nagbabasa ng data mula sa EEPROM at ipinapasa ito sa pamamagitan ng dout (data out) sa kasunod na alipin FPGA, pag -synchronize ng paglipat ng data gamit ang signal ng CCLK.Ang tapos na signal ay ginagamit upang ipahiwatig ang matagumpay na pagsasaayos, na may isang opsyonal na risistor ng pull-up na tinitiyak ang isang matatag na mataas na estado kapag kumpleto ang pagsasaayos.Ang XC1701L EEPROM ay kinokontrol ng master FPGA gamit ang CLK, data, CE (CHIP Paganahin), at pag -reset/OE (output paganahin) signal, tinitiyak na ang naka -imbak na data ng pagsasaayos ay tama na nakuha.Ang pamamaraan ng pagsasaayos na ito ay mahusay para sa pag -programming ng maraming mga FPGA gamit ang isang solong EEPROM, binabawasan ang pagiging kumplikado ng panlabas na mga kable at tinitiyak ang lahat ng mga aparato na makatanggap ng naka -synchronize na data ng pagsasaayos.

XCV200-6FG456C Mga pagtutukoy

|

I -type |

Parameter |

|

Tagagawa |

AMD Xilinx

|

|

Serye |

Virtex® |

|

Packaging |

Tray |

|

Bahagi ng Bahagi |

Lipas na |

|

Bilang ng mga lab/clbs |

1176 |

|

Bilang ng mga elemento/cell ng lohika |

5292 |

|

Kabuuang mga ram bits |

57344 |

|

Bilang ng I/O. |

284 |

|

Bilang ng mga pintuan |

236666 |

|

Boltahe - Supply |

2.375V ~ 2.625V |

|

Uri ng pag -mount |

Surface Mount |

|

Temperatura ng pagpapatakbo |

0 ° C ~ 85 ° C (TJ) |

|

Package / Kaso |

456-BBGA |

|

Package ng aparato ng supplier |

456-FBGA (23x23) |

|

Base Number Product |

XCV200 |

XCV200-6FG456C Application

Telecommunication at networking

Ang XCV200-6FG456C ay nangunguna sa mga aplikasyon ng telecommunication at networking dahil sa kakayahang hawakan ang mga high-speed data transmissions at kumplikadong mga gawain sa pagproseso ng signal.Ang mataas na bilang ng gate nito at matatag na mga kakayahan ng I/O ay nagbibigay -daan sa pagsuporta sa mga pag -andar tulad ng pagproseso ng packet, signal modulation/demodulation, at mga protocol ng pagwawasto ng error.

Digital Signal Processing (DSP)

Tamang -tama para sa mga aplikasyon ng DSP, ang FPGA na ito ay maaaring magsagawa ng mabilis at kumplikadong mga pagkalkula ng matematika na kinakailangan sa mga teknolohiya sa pagproseso ng audio at video.Kung ito ay para sa mga sistema ng multimedia, pagkilala sa boses, o mga serbisyo ng streaming, ang malakas na kakayahan sa pagproseso ng XCV200-6FG456C at naka-embed na suporta sa memorya na mahusay at de-kalidad na pagproseso ng signal.

Mga Sistema ng Kontrol sa Pang -industriya

Sa pang-industriya na automation, ang XCV200-6FG456C ay nagbibigay ng kinakailangang pagganap upang pamahalaan ang mga control system at automation network.Ang kakayahang magsagawa ng maraming mga gawain sa kontrol nang sabay -sabay habang tinitiyak ang mga oras ng pagtugon ay angkop para sa mga aplikasyon sa control control, robotics, at vision ng makina.

Mga instrumento sa medikal

Ang katumpakan at bilis ng FPGA ay mahusay sa medikal na imaging at diagnostic na kagamitan, kung saan tumutulong ito sa pagproseso ng mga kumplikadong algorithm para sa mga imaging aplikasyon tulad ng MRI, ultrasound, at mga pag -scan ng CT.Ang mga kakayahan ng XCV200-6FG456C ay matiyak na maaari itong hawakan ang mataas na data throughput at masalimuot na pagproseso na kinakailangan sa modernong teknolohiyang medikal.

Ang mga katulad na bahagi ng XCV200-6FG456C

XCV200-6FG456C Mga Hakbang sa Programming

Mga Hakbang sa Programming para sa XCV200-6FG456C:

1. Pagpasok sa Disenyo

Ang paunang yugto ng programming ng FPGA ay nagsasangkot ng pagtukoy sa digital na lohika at pag -andar ng iyong system.Magagawa ito gamit ang mga wika sa paglalarawan ng hardware (HDL) tulad ng VHDL o Verilog, kung saan nagsusulat ka ng code na tinukoy kung paano ang data ng FPGA at nakikipag -ugnay sa iba pang hardware.Ang mga tool sa pagpasok sa eskematiko na magagamit sa software ng disenyo ng FPGA tulad ng Xilinx ISE o vivado ay maaaring magamit.Ang pamamaraang ito ay nagsasangkot ng paglikha ng isang visual na representasyon ng lohika sa pamamagitan ng pag -drag at pagbagsak ng mga sangkap, na ang ilan ay nakakahanap ng mas madaling maunawaan kaysa sa code ng pagsulat.

2. Synthesis

Kapag nakumpleto ang disenyo, ang susunod na hakbang ay synthesis, kung saan ang isang tool tulad ng XLINX's XST (Xilinx Synthesis Technology) ay nagbabago sa iyong HDL code o disenyo ng eskematiko sa isang netlist.Inilalarawan ng netlist na ito ang circuit sa mga tuntunin ng mga pangkaraniwang mga sangkap na digital, tulad ng mga logic gate at rehistro.Ang proseso ng synthesis ay nagsasangkot din sa pag -optimize ng disenyo upang matugunan ang mga kinakailangan sa pagganap at mabawasan ang paggamit ng mapagkukunan para sa mahusay na operasyon ng FPGA.

3. Pagpapatupad

Ang proseso ng pagpapatupad ay nagsisimula sa pagsasalin, pagsasama -sama ng iyong disenyo sa mga file ng pagpilit na tumutukoy sa mga parameter tulad ng mga frequency ng orasan at mga takdang -PIN.Kasunod ng pagsasalin, ang yugto ng pagmamapa ay nagtatalaga ng mga elemento ng iyong netlist sa mga tiyak na pisikal na mapagkukunan sa FPGA, tulad ng mga look-up table (LUTS) at flip-flops.Ang phase ng paglalagay at pagruruta pagkatapos ay tinutukoy ang mga pisikal na lokasyon ng bawat sangkap sa loob ng arkitektura ng FPGA at itinatag ang mga koneksyon sa pagitan nila sa pamamagitan ng mga ma -program na magkakaugnay na mapagkukunan.Ang yugtong ito ay mahusay para sa pagkamit ng nais na mga sukatan ng pagganap, kabilang ang mga dalas ng orasan.

4. henerasyon ng bitstream

Matapos ang matagumpay na paglalagay at pagruruta, ang tool ay bumubuo ng isang bitstream, isang file ng pagsasaayos ng binary na naglalaman ng lahat ng impormasyon sa programming para sa FPGA.Madalas na inirerekomenda na gayahin ang pangwakas na post-placement upang matiyak na ang bitstream ay kumikilos tulad ng inaasahan sa ilalim ng mga kondisyon.Ang hakbang na ito ng pagpapatunay ay nakakatulong upang maiwasan ang mga potensyal na isyu sa panahon ng aktwal na operasyon.

5. Pag -configure

Ang pangwakas na hakbang ay nagsasangkot ng pag -load ng bitstream sa FPGA gamit ang iba't ibang mga pamamaraan ng pagsasaayos.Ang mode na alipin-serial, isang simple at epektibong pagpipilian, ay nag-configure ng FPGA sa pamamagitan ng isang panlabas na aparato ng master na nagpapadala ng data nang serial.Sa master-serial mode, binabasa ng FPGA autonomously ang bitstream mula sa isang nakalakip na serial prom.Para sa mga high-speed na pagsasaayos, pinapayagan ng SelectMap mode ang isang panlabas na microprocessor na mag-load ng data sa FPGA nang mabilis.Bilang karagdagan, ang mode ng JTAG ay ginagamit hindi lamang para sa programming kundi pati na rin para sa pagsubok at pag-debug, paggamit ng isang karaniwang interface para sa pag-programming ng in-system at pagsubok sa hangganan.

XCV200-6FG456C Mga Bentahe

Pagganap

Ang serye ng Xilinx Virtex, kung saan nabibilang ang XCV200-6FG456C, ay na-optimize para sa pagganap ng high-speed, na nag-aalok ng mga rate ng orasan ng system na hanggang sa 200 MHz.Ginagawa nitong angkop para sa mga aplikasyon na nangangailangan ng mabilis na pagproseso ng data, tinitiyak ang mahusay na paghawak ng mga kumplikadong algorithm at mga operasyon na may mataas na bilis tulad ng telecommunication, pagproseso, at multimedia.

Suporta sa I/O.

Sinusuportahan ng FPGA na ito ang isang malawak na hanay ng mga pamantayan sa pag -input/output, kabilang ang LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT, at AGP.Ang nasabing malawak na suporta sa I/O ay nagbibigay-daan sa XCV200-6FG456C na pagsamahin nang walang putol sa iba't ibang mga sangkap ng system, pagpapahusay ng utility nito sa magkakaibang mga digital na ekosistema.Ang kakayahang umangkop na ito ay nagbibigay -daan upang iakma ang FPGA sa iba't ibang mga kondisyon ng interface nang walang mga pagbabago sa system.

Pamamahala ng orasan

Ang XCV200-6FG456C ay nagsasama ng maraming mga loop na naka-lock (DLL) para sa pamamahagi ng orasan at pamamahala sa loob ng system.Ang mga DLL na ito ay tumutulong sa pagpapabuti ng tiyempo ng system at pagiging maaasahan sa pamamagitan ng pagbibigay ng tumpak na mga signal ng orasan na kinakailangan para sa magkakasabay na operasyon.Mahalaga ang tampok na ito sa pagbabawas ng mga error sa system at pagpapahusay ng pangkalahatang pagganap, lalo na sa mga kumplikadong disenyo na nangangailangan ng tumpak na tiyempo at pag -synchronise.

Kakayahang umangkop sa disenyo

Sa pamamagitan ng 1,176 na-configure na mga bloke ng lohika at 5,292 logic cells, ang XCV200-6FG456C ay nag-aalok ng malaking mapagkukunan ng lohika na may kakayahang ipatupad ang isang magkakaibang hanay ng mga pag-andar.Mula sa simpleng lohika ng pandikit hanggang sa masalimuot na mga digital system, sinusuportahan ng FPGA ang kumplikadong mga kinakailangan sa disenyo, na ginagawang perpekto para sa mga aplikasyon sa pasadyang computing, pagproseso ng digital signal, at prototyping.

Mabilis na prototyping

Ang mga FPGA tulad ng XCV200-6FG456C ay kilala sa kanilang kakayahang suportahan ang mabilis na prototyping.Pinapayagan ng aparatong ito para sa mabilis na mga iterasyon ng disenyo at maaaring mai-configure na in-field, na kung saan ay isang kalamangan para sa mga siklo ng pag-unlad dahil binabawasan nito ang oras-sa-merkado.Ito rin ay umaangkop nang mahusay sa pagbabago ng mga kinakailangan o pag-update sa mga pagtutukoy ng proyekto, tinitiyak na ang pangwakas na mga produkto ay napapanahon sa pinakabagong mga pamantayan sa teknolohikal.

Kakayahang pagsasama

Ang mga kakayahan ng pagsasama ng XCV200-6FG456C ay pinadali ang pagsasama-sama ng maraming mga discrete na sangkap sa isang solong chip.Ang pagsasama na ito ay maaaring humantong sa nabawasan na pagiging kumplikado ng system, mas mababang pagkonsumo ng kuryente, at pagtitipid ng gastos.Sa pamamagitan ng pag -minimize ng bilang ng mga magkahiwalay na sangkap na kinakailangan, ang FPGA na ito ay pinasimple ang mga proseso ng disenyo at pinapabuti ang pagiging maaasahan at pagiging compactness ng pangkalahatang sistema.

XCV200-6FG456C Mga Dimensyon ng Packaging

Ang XCV200-6FG456C ay isang patlang na maaaring ma-program na gate array (FPGA) mula sa serye ng Virtex® ng AMD, na nakalagay sa isang 456-ball fine-pitch ball grid array (FBGA) package.

At Uri ng Package: 456-fbga

At Laki ng pakete: 23 mm x 23 mm

At Ball Pitch: 1.0 mm

XCV200-6FG456C Tagagawa

Ang XCV200-6FG456C ay isang patlang na maaaring ma-program na gate array (FPGA) na orihinal na binuo ng Xilinx, isang kumpanya na kilala para sa mga high-performance na mga aparato na lohika.Kasunod ng pagkuha ni Xilinx ni AMD, Ang XCV200-6FG456C ay nauugnay na ngayon sa AMD bilang kasalukuyang tagagawa nito.Gayunpaman, ang modelong FPGA na ito ay hindi na ginagamit at hindi na sa paggawa.Patuloy na sinusuportahan ng AMD ang mga mas bagong arkitektura ng FPGA na may pinahusay na pagganap, kahusayan ng kuryente, at pinalawak na kahabaan ng buhay, na ginagawang mas gusto ang mga modernong alternatibo para sa mga bagong disenyo.

Konklusyon

Ang XCV200-6FG456C ay isang maraming nalalaman at high-speed FPGA, kapaki-pakinabang para sa maraming mga aplikasyon ng teknolohiya.Habang hindi na ito ginagawa, ito ay isang mahusay na pagpipilian para sa mga mas matatandang sistema na nangangailangan ng maaasahang pagganap.Sakop ng gabay na ito ang disenyo nito, mga hakbang sa programming, at praktikal na paggamit, na ginagawang mas madaling maunawaan kung paano ito gumagana at kung paano ito magagamit.Habang magagamit ang mga mas bagong FPGA, maaari mong gamitin ang kaalamang ito upang piliin ang tamang FPGA para sa iyong mga pangangailangan at pagbutihin ang mga digital na disenyo.

Datasheet PDF

XCV200-6FG456C Datasheets:

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Ano ang pagkonsumo ng kuryente ng XCV200-6FG456C?

Ang XCV200-6FG456C ay nagpapatakbo sa 2.5V, na may saklaw ng boltahe na 2.375V hanggang 2.625V.Ang pagkonsumo ng kuryente ay nakasalalay sa paggamit ng lohika at dalas ng orasan, ngunit bilang isang mas matandang FPGA, maaaring hindi gaanong mas mahusay ang kapangyarihan kaysa sa mga mas bagong aparato ng Xilinx.Ang wastong pamamahala ng kuryente at pag -iwas sa init ay dapat isaalang -alang.

2. Paano ihahambing ang XCV200-6FG456C sa XCV200-6FG256C?

Ang XCV200-6FG456C ay may isang mas malaking pakete (456-ball FBGA) kumpara sa XCV200-6FG256C (256-ball FBGA), na nag-aalok ng higit na I/O pin (284 kumpara sa 172) at potensyal na mas mahusay na pagganap para sa mga aplikasyon na nangangailangan ng malawak na interface.Kung ang iyong disenyo ay umaasa sa higit pang mga kakayahan sa I/O, ang XCV200-6FG456C ay ang mas mahusay na pagpipilian.

3. Maaari ko bang i-reprogram ang xcv200-6fg456c nang maraming beses?

Oo, ang XCV200-6FG456C ay isang SRAM na nakabase sa FPGA, nangangahulugang maaari itong muling ma-reprogrammed ng isang walang limitasyong bilang ng beses hangga't ang kapangyarihan ay ibinibigay.Gayunpaman, kakailanganin mo ang panlabas na di-pabagu-bago ng memorya (EEPROM o FLASH) upang mapanatili ang bitstream pagkatapos ng isang ikot ng kuryente.

4. Sinusuportahan ba ng XCV200-6FG456C ang high-speed serial na komunikasyon?

Sinusuportahan ng XCV200-6FG456C ang maraming mga pamantayan sa I/O tulad ng LVTTL, LVCMOS, PCI, GTL, HSTL, at SSTL, ngunit wala itong built-in na high-speed na mga serdes (serializer/deserializer) o mga transceiver tulad ng mga modernong fpgas.Para sa mga application na nangangailangan ng high-speed serial link (hal., PCIE, Gigabit Ethernet, o HDMI), isaalang-alang ang mga mas bagong modelo ng FPGA.

5. Paano ihahambing ang XCV200-6FG456C sa mga mas bagong modelo ng FPGA?

Ang XCV200-6FG456C ay kabilang sa isang mas matandang henerasyon ng mga FPGA.Kung ikukumpara sa mga modernong FPGA ng Virtex, mayroon itong mas mababang bilang ng gate, mas mabagal na bilis ng orasan, at limitadong kahusayan ng kuryente.Ang mga mas bagong modelo ay nag -aalok ng mas mataas na density ng lohika, mas naka -embed na memorya, mga advanced na bloke ng DSP, at mas mababang pagkonsumo ng kuryente, na ginagawang mas mahusay para sa mga modernong aplikasyon.

Ang AD73322AR pinout, mga tampok, at mga teknikal na detalye ay ipinaliwanag

sa 2025/03/21

EP20K100EFC324-1X FPGA: Mga Tampok, Mga Pagtukoy, Aplikasyon, at Gabay sa Programming

sa 2025/03/20

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147780

-

USB-C pinout at mga tampok

sa 2000/04/18 112041

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111352

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83798

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79604

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66982

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63113

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63048

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54097

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52198