XC2S100E-6FTG256C FPGA Gabay: Mga pagtutukoy, tampok, at aplikasyon

Ang gabay na ito ay galugarin ang XC2S100E-6FTG256C, isang epektibong gastos at maraming nalalaman FPGA na dinisenyo para sa mga naka-embed na system, pang-industriya na kontrol, at mga digital na aplikasyon ng lohika.Sa pamamagitan ng isang mayamang kumbinasyon ng mga cell ng lohika, i -block at ipinamamahagi ang RAM, at mataas na kakayahang umangkop sa I/O, nagsisilbi itong isang maaasahang solusyon para sa parehong mga modernong aplikasyon at suporta sa sistema ng legacy.Sa gabay na ito, malalaman mo kung ano ang magagawa ng FPGA na ito, kung paano ito itinayo, kung paano gamitin ito, at kung bakit ito ay isang mahusay na pagpipilian ngayon.Catalog

XC2S100E-6FTG256C Pangkalahatang-ideya

Ang XC2S100E-6FTG256C ay isang mataas na pagganap, murang FPGA mula sa pamilya ng Spartan-IIE, na naayon para sa mga naka-embed na system, pang-industriya na automation, at mga disenyo ng digital na pagproseso ng digital.Sa pamamagitan ng isang kapasidad ng 100,000 mga pintuan ng system at 2,700 mga cell ng lohika, sinusuportahan ng aparatong ito ang maraming nalalaman na mga aplikasyon ng lohika habang pinapanatili ang mahusay na pagkonsumo ng kuryente sa pamamagitan ng 1.8V core nito.Isinasama nito ang 40 kbits ng block ram at 38,400 bits ng ipinamamahaging RAM, na nag -aalok ng mga taga -disenyo ng mga pagsasaayos ng memorya.Ang pagpapatakbo sa bilis hanggang sa 275 MHz, sinusuportahan nito ang mabilis na pagproseso ng data para sa mga gawain na kritikal sa oras.Dinisenyo gamit ang 0.15 µM CMOS na teknolohiya, ang -6 bilis ng grado ay nagpapahiwatig ng isang maaasahang tier ng pagganap na angkop para sa karamihan sa mga pangunahing aplikasyon.Ang pamilyang Spartan-IIE, na kinabibilangan ng XC2S100E-6FTG256C, ay saklaw sa density ng lohika mula 50k hanggang 600k na mga pintuan at mga tampok na kinakailangang mga tool tulad ng apat na DLL para sa advanced na control ng orasan, nakatuon na lohika para sa mga function ng aritmetika, at pagiging tugma sa 3.3V PCI/Cardbus interface.

Kung naghahanap ka ng maaasahang mga solusyon sa FPGA, ang XC2S100E-6FTG256C ay isang solidong pagpipilian, huwag mag-atubiling ilagay ang iyong mga order na bulk sa amin anumang oras

XC2S100E-6FTG256C Mga Tampok

Kapasidad ng lohika: Ang XC2S100E-6FTG256C ay nag-aalok ng 100,000 mga pintuan ng system, na nagbibigay ng sapat na lohika para sa katamtamang kumplikadong mga digital na disenyo.Ang 2,700 logic cells nito ay nagsisilbing core configurable logic blocks na nagbibigay-daan sa isang malawak na iba't ibang mga function na tinukoy ng gumagamit.

Naka -embed na memorya: Kasama sa FPGA na ito ang 40 kbits ng kasabay na block ram, na angkop para sa buffering, pansamantalang imbakan ng data, o pagpapatupad ng mga FIFO at iba pang mga istruktura ng memorya sa loob ng disenyo ng lohika.

Ipinamamahagi na RAM: Bilang karagdagan sa pag -block ng RAM, nag -aalok ito ng 38,400 piraso ng ipinamamahaging RAM na maaaring magamit para sa mga compact na elemento ng memorya na kumalat sa tela ng lohika.Ito ay kapaki -pakinabang para sa pagpapatupad ng mga maliit na talahanayan ng lookup o data ng pagsasaayos na malapit sa pagproseso ng lohika.

Gumagamit i/o pin: Ang aparato ay nagbibigay ng hanggang sa 176 pangkalahatang-layunin I/O pin, na nagpapahintulot sa interface na may isang malawak na hanay ng mga peripheral, panlabas na aparato ng memorya, o iba pang mga IC sa system.

Mataas na dalas ng operating: Sa pamamagitan ng isang maximum na panloob na rate ng orasan na 275 MHz, ang XC2S100E ay nagbibigay-daan sa mabilis na pagproseso ng signal at sumusuporta sa mga operasyon na may bilis na kinakailangan sa mga control system, komunikasyon, at pagkuha ng signal.

Pangunahing boltahe: Ang pagpapatakbo ng isang pangunahing boltahe ng 1.8V, ang aparato ay idinisenyo para sa mababang pagkonsumo ng kuryente habang pinapanatili pa rin ang sapat na pagganap para sa mga aplikasyon ng mid-range.

Teknolohiya ng Proseso: Ginawa gamit ang isang proseso ng 0.15-micron CMOS, binabalanse ng aparato na ito ang density ng pagsasama na may kahusayan ng thermal at nagbibigay ng matatag na operasyon sa ilalim ng mga kondisyon ng industriya.

Bilis ng grado: Ang "-6" bilis ng grado ay nagpapahiwatig ng karaniwang variant ng pagganap sa loob ng serye ng Spartan-IIE.Nag -aalok ito ng isang balanseng kumbinasyon ng bilis at kahusayan ng kapangyarihan na angkop para sa isang malawak na hanay ng mga digital na disenyo.

XC2S100E-6FTG256C block diagram

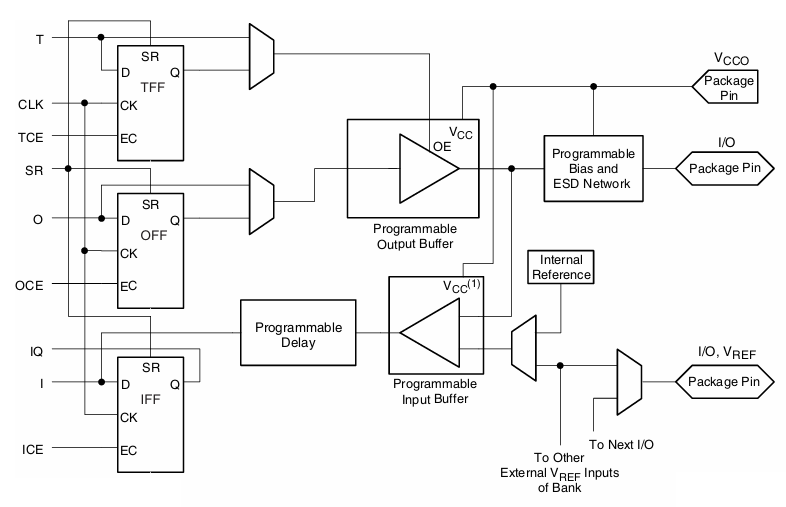

Input/Output Block (IOB)

Ipinapakita ng diagram na ito kung paano ang XC2S100E-6ftg256C FPGA ay humahawak ng mga signal na papasok at labas ng I/O pin.Hinahayaan ka ng input/output block (IOB) kung kailan at kung paano gumagalaw ang data sa pagitan ng FPGA at sa labas ng mundo.Mayroon itong magkahiwalay na mga seksyon para sa pag -input, output, at kontrol ng lohika.Sa output side, ang mga signal ay nagmula sa mga flip-flops (TFF at OFF), na nag-iimbak ng data.Ang mga ito ay kinokontrol ng isang orasan (CLK), paganahin ang mga signal (TCE, OCE), at isang set/reset input (SR).Ang data ng output ay dumadaan sa isang programmable buffer na nagtutulak ng signal sa PIN.Ang buffer na ito ay maaaring mai -tono para sa lakas at bilis at may kasamang proteksyon laban sa static na kuryente (ESD).Para sa mga input, ang mga signal mula sa pin ay dumaan sa isang pagkaantala ng bloke at pagkatapos ay isang programmable input buffer.Maaaring ayusin ng buffer na ito kung paano binabasa nito ang signal, depende sa mga antas ng boltahe at pamantayan.Ang isang sanggunian na boltahe (VREF) ay tumutulong na magpasya kung paano iproseso ang input, lalo na kapag gumagamit ng ilang mga uri ng signal.

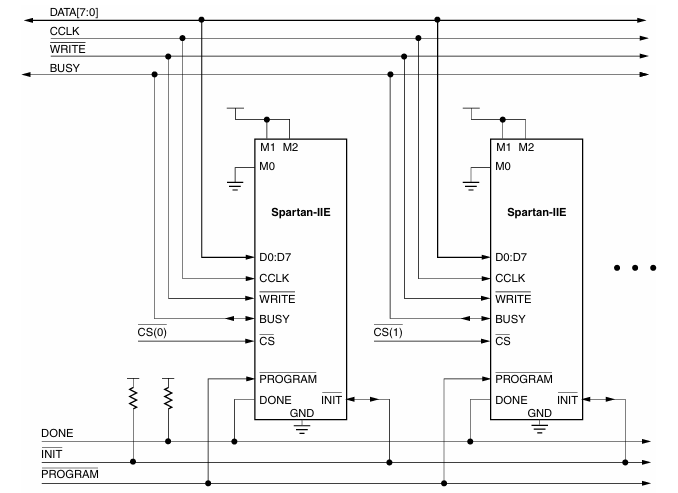

Alipin na kahanay na mode

Inilalarawan ng diagram ang pag-configure ng parallel mode ng alipin para sa maramihang XC2S100E-6ftg256C Spartan-IIE fPGA mula sa AMD Xilinx.Sa pag-setup na ito, maraming mga FPGA ang na-program nang sabay-sabay gamit ang isang ibinahaging 8-bit data bus (data [7: 0]), isang karaniwang pagsasaayos ng orasan (CCLK), at mga signal ng kontrol tulad ng pagsulat at programa.Ang bawat FPGA ay tumatanggap ng data ng pagsasaayos nang magkatulad, na nagpapahintulot sa mas mabilis na programming kumpara sa mga serial mode.

Ang bawat FPGA ay may mga M0-M2 mode na pinatay, na itinatakda ito sa mode na paralel ng alipin, kung saan ang data ng pagsasaayos ay itinulak sa aparato ng isang panlabas na magsusupil.Ang linya ng CS (Chip Select) ay ginagamit upang paganahin ang mga indibidwal na aparato, tinitiyak lamang ang isang FPGA na aktibo sa panahon ng pagsasaayos upang maiwasan ang pagtatalo ng bus.Ang abala at tapos na mga signal ay makakatulong na masubaybayan ang katayuan ng bawat aparato sa panahon ng proseso, habang ang init pin ay ibinahagi upang ayusin ang pagsisimula sa lahat ng mga aparato.Pull-up resistors sa tapos na at init tiyakin ang wastong mga antas ng lohika kapag hindi aktibo.

XC2S100E-6FTG256C Mga pagtutukoy

|

I -type |

Parameter |

|

Tagagawa |

AMD/Xilinx |

|

Serye |

Spartan®-iie |

|

Packaging |

Tray |

|

Bahagi ng Bahagi |

Lipas na |

|

Bilang ng mga lab/clbs |

600 |

|

Bilang ng mga elemento/cell ng lohika |

2700 |

|

Kabuuang mga ram bits |

40960 |

|

Bilang ng I/O. |

182 |

|

Bilang ng mga pintuan |

100000 |

|

Boltahe - Supply |

1.71V ~ 1.89V |

|

Uri ng pag -mount |

Surface Mount |

|

Temperatura ng pagpapatakbo |

0 ° C ~ 85 ° C (TJ) |

|

Package / Kaso |

256-lbga |

|

Package ng aparato ng supplier |

256-ftbga (17x17) |

|

Base Number Product |

XC2S100E |

XC2S100E-6FTG256C Application

Mga Sistema ng Pang -industriya at Kontrol

Ang XC2S100E-6FTG256C ay mainam para sa pagpapatupad ng mga scheme ng control-intensive control sa mga pang-industriya na kapaligiran.Maaari itong pamahalaan ang pagproseso ng signal, mga loop ng control ng motor, at ma -program na lohika para sa mga robotics at mga sistema ng pagmamanupaktura.Ang mabilis na I/O at maaasahang tiyempo ay angkop para sa pakikipag -ugnay sa mga sensor, actuators, at mga tagapangasiwa ng pangangasiwa.

Naka -embed na mga system at SOC prototyping

Pinapayagan ka ng FPGA na lumikha ka ng mga pasadyang naka-embed na logic platform at prototype system-on-chip (SOC) na mga arkitektura.Sa pamamagitan ng reprogrammable logic at ipinamamahagi na memorya, nakakatulong ito na gayahin ang mga cores ng pagproseso, mga interface ng peripheral, at pasadyang mga bloke ng digital na IP nang mabilis at abot -kayang.

Automotive Electronics

Ang aparato ay maaaring magamit sa mga sasakyan para sa mga gawain tulad ng pamamahala ng mga digital dashboard, in-sasakyan na mga sistema ng libangan, at pagproseso ng mababang antas ng signal sa mga sistema ng pagtulong sa driver.Ang kahusayan ng kapangyarihan nito at matatag na mga disenyo ng I/O ay sumusuporta sa mga disenyo ng automotive-grade na nangangailangan ng pangmatagalang pagiging maaasahan.

Mga platform sa edukasyon at pagsasanay

Sa pamamagitan ng madaling lapitan na density ng lohika at naa-access na toolchain (ISE Design Suite), ang XC2S100E-6FTG256C ay mahusay para sa pag-aaral ng digital na disenyo, ang VHDL/verilog programming, at mga diskarte sa pagsasama ng system.

Pagpapanatili ng legacy system at pag -upgrade

Maraming mga system na itinayo noong unang bahagi ng 2000s na ginamit ang Spartan-IIE FPGA na tulad nito.Ang XC2S100E-6FTG256C ay patuloy na mabuti para sa pagsuporta at pagpapanatili ng mga sistemang ito, pagpapagana ng pag-aayos o pagpapahusay nang walang buong muling pagdisenyo, tinitiyak ang pagiging tugma ng software at hardware.

Ang mga katulad na bahagi ng XC2S100E-6FTG256C

Ang XC2S100E-6PQG208C ay isang miyembro ng parehong pamilya ng Spartan-IIE at nag-aalok ng parehong kapasidad ng lohika at mga pagtutukoy ng pagganap bilang XC2S100E-6FTG256C, kabilang ang 2,700 logic cells at 100,000 mga gate ng system.Ito ay nakabalot sa isang 208-pin plastic quad flat pack (PQFP), na ginagawang angkop para sa mga disenyo na mas gusto o nangangailangan ng mga leaded packages para sa mas madaling inspeksyon at rework.Ito ay isang malakas na alternatibo kung ikaw ay lumilipat sa malayo sa BGA packaging at nangangailangan ng isang mas mababang gastos o mas madaling mag-folder na bakas ng paa habang pinapanatili ang buong katumbas na pag-andar.

Ang bahaging ito ay halos magkapareho sa XC2S100E-6PQG208C, naiiba sa mga posibleng marking o sourcing, ngunit nakalagay pa rin sa parehong 208-pin na PQFP package.Pinapanatili nito ang parehong -6 na bilis ng grado at pagganap ng elektrikal, na ginagawa itong isang alternatibong drop -in sa mga tuntunin ng pag -uugali ng lohika para sa mga disenyo na gumagamit ng bakas ng PQ208.Ang pagpipiliang ito ay mahusay kapag kinakailangan ang kakayahang umangkop sa sourcing, dahil pinapayagan nito ang pagiging tugma sa parehong layout ng PCB habang pinapalawak ang iyong mga pagpipilian sa tagapagtustos.

Ang XC2S100E-6FT256C ay nagbabahagi ng eksaktong bilang ng BGA PIN (256 bola) bilang orihinal na XC2S100E-6FTG256C, bagaman maaaring magkakaiba ito sa thermal o packaging specs (e.g., "FT" kumpara sa "FTG").Elektriko at functionally, halos magkapareho ito, at dahil nananatili ito sa loob ng parehong kategorya ng BGA at pamilya ng lohika, ito ang pinaka direktang kapalit mula sa isang mekanikal at pananaw sa pagganap.Kung naghahanap ka ng kaunting muling pagdisenyo ng PCB, ang bahaging ito ay malamang na ang pinaka -walang tahi na kapalit.

XC2S100E-6FTG256C Mga Hakbang sa Programming

1. Pag -entry sa Disenyo at Synthesis: Upang simulan ang pag-programming ng XC2S100E-6FTG256C, kailangan mo munang lumikha ng digital na disenyo ng lohika gamit ang isang Hardware Description Language (HDL) tulad ng VHDL o Verilog.Ang hakbang na ito ay isinasagawa gamit ang Xilinx ISE Design Suite o isang katulad na tool ng synthesis.Matapos isulat ang disenyo, na-synthesize upang mai-convert ang mataas na antas ng lohika sa isang listahan ng antas ng gate.Ang tool ng synthesis pagkatapos ay bumubuo ng isang bitstream file (karaniwang may isang .bit extension), na naglalaman ng data ng pagsasaayos na kinakailangan upang i -program ang FPGA.

2. Piliin ang mode ng pagsasaayos: Sinusuportahan ng pamilyang Spartan-IIE ang iba't ibang mga mode ng pagsasaayos kabilang ang serial serial, master serial, alipin kahanay, master kahanay, at jtag (hangganan ng pag-scan).Dapat mong piliin ang mode na nababagay sa pag -setup ng iyong system sa pamamagitan ng tama na pagtatakda ng mga mode na pin (M0, M1, M2).Ang mga pin na ito ay nagdidikta kung paano mai-load ng FPGA ang data ng pagsasaayos nito pagkatapos ng power-up o i-reset.Halimbawa, ang mode ng JTAG ay karaniwang ginagamit para sa pag-debug ng in-system at kakayahang umangkop sa panahon ng pag-unlad.

3. Ikonekta ang programming hardware: Depende sa napiling mode ng pagsasaayos, ikonekta ang naaangkop na hardware.Para sa JTAG programming, gumamit ng isang JTAG programmer tulad ng Xilinx platform cable USB.Nangangailangan ito ng wastong koneksyon sa mga pin ng JTAG: TDI (data ng pagsubok sa), TDO (data ng pagsubok), TCK (test clock), at TMS (Test Mode Select).Gayundin, tiyakin na ang PIN ng programa ay wired upang payagan ang muling pagpapalakas.Ang wastong saligan at mga koneksyon sa VCC ay mahalaga para sa matatag na operasyon sa panahon ng pagsasaayos.

4. Program ang FPGA: Gamit ang tool na epekto ng Xilinx (mula sa ISE suite), i -load ang .bit file sa FPGA.Kung gumagamit ng JTAG mode, ang epekto ay nakikipag -usap sa FPGA sa pamamagitan ng interface ng JTAG.Sa loob, ang proseso ay nagsasama ng pag-load ng pagtuturo ng CFG_IN, paglilipat ng bitstream sa pamamagitan ng estado ng shift-dr sa FPGA sa pamamagitan ng TDI, at pag-trigger ng pagsasaayos sa pagtuturo ng JSTART.Kapag ang bitstream ay ganap na na -load, ang FPGA ay gumagalaw sa normal na operasyon.Tiyakin na ang tapos na pin ay mataas, na nagpapahiwatig ng matagumpay na pagsasaayos.

5. Patunayan ang pagsasaayos : Pagkatapos ng programming, mahalaga na kumpirmahin na ang aparato ay wastong natanggap ang pagsasaayos.Ang pinakasimpleng tseke ay ang pag -obserba ng tapos na pin, na dapat pumunta nang mataas pagkatapos ng isang matagumpay na pagkarga ng bitstream.Bilang karagdagan, ang epekto ng software ay maaaring magsagawa ng isang proseso ng pagbabasa o pag -verify upang ihambing ang na -load na bitstream na may orihinal na file, tinitiyak na walang mga pagkakamali na naganap sa panahon ng paghahatid.

XC2S100E-6FTG256C Mga kalamangan

Mababang pagkonsumo ng kuryente

Ang XC2S100E-6FTG256C ay nagpapatakbo sa isang pangunahing boltahe ng 1.8V lamang, na binabawasan ang pagkonsumo ng kuryente kumpara sa mas matandang mga FPGA na tumatakbo sa 2.5V o mas mataas.Ginagawa nitong isang ginustong pagpipilian para sa mga sistema na pinatatakbo ng baterya o thermally na napipilitan, kung saan kinakailangan ang pamamahala ng init at pagpapalawak ng kahusayan ng kuryente.Ang mas mababang boltahe ay hindi lamang nagpapabuti sa kahusayan ng enerhiya ngunit nakakatulong din sa pag -minimize ng laki at gastos ng mga sangkap ng regulasyon ng panlabas na kuryente.

Mataas na bilang ko

Ang FPGA na ito ay nagbibigay ng hanggang sa 182 I/O pin, na nag -aalok ng isang malawak na hanay ng mga puntos ng koneksyon para sa mga peripheral at mga interface ng system.Pinapayagan ng mataas na bilang na ito ang XC2S100E-6FTG256C upang mahawakan ang kumplikadong pag-ruta ng signal at maraming mga panlabas na aparato, tulad ng mga interface ng memorya, mga bus ng data, o mga module ng komunikasyon.Sa mga system na humihiling ng maraming mga magkakatulad na koneksyon o halo -halong mga interface ng signal, binabawasan ng aparatong ito ang pangangailangan para sa karagdagang multiplexing o panlabas na logic ng pandikit.

Pinahusay na mga mapagkukunan ng lohika

Sa pamamagitan ng 2,700 mga cell ng lohika at isang malaking bilang ng mga naka -configure na mga bloke ng lohika (CLB), ang aparatong ito ay nagbibigay ng maraming mga mapagkukunan para sa pagbuo ng mga sopistikadong digital circuit.Sinusuportahan nito ang mga katamtamang disenyo ng katamtaman, tulad ng mga naka-embed na controller, pasadyang mga landas ng data, at mga kadena sa pagproseso ng signal.Kumpara sa mga naunang aparato ng Spartan o CPLDS, ang FPGA na ito ay nag -aalok ng isang kapansin -pansin na pagpapabuti sa lohika density at kakayahang umangkop sa disenyo nang walang pagtaas ng gastos.

Pinagsamang block ram

Ang XC2S100E-6FTG256C ay may kasamang 40 kbits ng naka-embed na block ram, na nagbibigay-daan sa pag-iimbak ng pansamantalang data, buffer, o mga talahanayan ng lookup nang direkta sa loob ng FPGA.Ang naka -embed na memorya na ito ay binabawasan ang pangangailangan para sa mga panlabas na chips ng RAM, pagbaba ng gastos sa BOM at pagpapabuti ng throughput ng data.Ito ay kapaki -pakinabang para sa mga application tulad ng pagkuha ng data, buffering sensor input, o pansamantalang data caching sa panahon ng pagproseso.

XC2S100E-6FTG256C Mga Dimensyon ng Packaging

At Uri ng Package: 256-ball fine-pitch manipis na bola grid array (ftbga)

At Laki ng katawan: 17 mm × 17 mm

At Ball Pitch: Karaniwang 1.0 mm

At Uri ng pag -mount: Surface mount

At Taas ng pakete: Humigit -kumulang na 1.4 mm

At Antas ng Sensitivity ng kahalumigmigan (MSL): Oo, sensitibo sa kahalumigmigan

At Standard packaging: Ibinigay sa mga tray

XC2S100E-6FTG256C Tagagawa

Ang XC2S100E-6FTG256C ay ginawa ng AMD, kasunod ng pagkuha ng Xilinx, ang orihinal na developer ng pamilyang Spartan-IIE FPGA.Ang AMD, isang pandaigdigang pinuno sa high-performance computing at semiconductor na teknolohiya, ngayon ay pinangangasiwaan ang kumpletong portfolio ng mga aparato na naka-program na naka-program na xilinx, kabilang ang mga produktong legacy tulad ng XC2S100E-6FTG256C.Ang paglipat na ito ay nagpalakas sa pagkakaroon ng AMD sa FPGA at adaptive computing market, tinitiyak ang patuloy na suporta at pagsasama ng pamana ng pagbabago ng Xilinx sa mas malawak na mga solusyon sa antas ng system.Habang ang XC2S100E-6FTG256C ay opisyal na inuri bilang hindi na ginagamit, ang AMD ay patuloy na mapadali ang suporta ng lifecycle, teknikal na dokumentasyon, at mga mapagkukunan ng paglipat para sa mga disenyo ng legacy na itinayo sa paligid ng mga aparato ng Spartan-IIE.

Konklusyon

Ang XC2S100E-6FTG256C ay isang malakas at murang FPGA na nagbibigay sa iyo ng 100,000 mga pintuan at 2,700 na mga bloke ng lohika upang makabuo ng mga pasadyang digital na pag-andar.Ito ay may built-in na memorya, maraming mga input/output pin, at mabilis na tumatakbo hanggang sa 275 MHz.Gumagamit lamang ito ng 1.8 volts, kaya nakakatipid ito ng kapangyarihan.Ang chip na ito ay mahusay para sa mga makina sa mga pabrika, mga sistema ng kotse, mga proyekto ng mag -aaral, at pag -aayos ng mga lumang disenyo.Maaari ka ring pumili ng iba pang mga katulad na bersyon kung kailangan mo ng ibang pakete.Kahit na hindi ito isang bagong bahagi, gumagana pa rin ito nang maayos at suportado ng AMD.Ito ay isang matalinong pagpili para sa sinumang nagtatayo o nag -aayos ng mga digital system.

Datasheet PDF

XC2S100E-6FTG256C Datasheets:

Spartan, Virtex, XC17V00 24/APR/2013.PDF

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Paano ihahambing ang XC2S100E-6FTG256C sa mga mas bagong FPGA tulad ng Spartan-6 o Artix-7?

Kung ikukumpara sa mga mas bagong pamilya, ang XC2S100E-6FTG256C ay may mas kaunting mga cell ng lohika, mas mababang kapasidad ng memorya, at mas mabagal na I/O.Gayunpaman, mas epektibo ang gastos para sa simple o katamtamang mga aplikasyon, at ang mature na disenyo nito ay ginagawang matatag at maayos na na-dokumentado.

2. Anong mga tool sa programming ang kailangan ko para sa pag-configure ng XC2S100E-6FTG256C?

Kakailanganin mo ang Xilinx ISE Design Suite at isang katugmang programming cable tulad ng Xilinx platform cable USB.Pinapayagan ka ng mga tool na ito na lumikha ng bitstream at i -upload ito sa pamamagitan ng JTAG o iba pang mga suportadong mode.

3. Maaari bang hawakan ng FPGA ang parehong 3.3V at 2.5V I/O signaling?

Oo, ang XC2S100E-6FTG256C ay sumusuporta sa iba't ibang mga pamantayan sa I/O, kabilang ang LVCMOS at LVTTL, at maaaring mai-configure upang gumana kasama ang parehong 3.3V at 2.5V na nag-sign sa pamamagitan ng mga setting ng IOB at mga input ng VREF.

4. Ano ang pagkonsumo ng kuryente ng XC2S100E-6FTG256C sa ilalim ng karaniwang pag-load?

Sa ilalim ng tipikal na pag -load, ang pagkonsumo ng kuryente ay medyo mababa dahil sa kanyang 1.8V core boltahe.Ang eksaktong lakas ay nakasalalay sa aktibidad ng lohika at dalas ng orasan, ngunit ito ay angkop para sa mga thermally constrained system.

5. Maaari bang ma-program nang sabay-sabay ang mga aparato ng XC2S100E-6FTG256C?

Oo, gamit ang mode na kahanay ng alipin, maraming mga aparato ang maaaring mai -configure nang sabay -sabay sa isang nakabahaging data ng bus.Pinapabilis nito ang pagsubok sa paggawa o pagsisimula ng system sa mga aplikasyon ng malakihan.

XCS30-3VQ100C FPGA: Mga Tampok, Programming at Alternatibo

sa 2025/05/7

AD8130AR Amplifier Guide: Mga Tampok, Pinout, Application at Datasheet

sa 2025/05/6

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/19 147782

-

USB-C pinout at mga tampok

sa 2000/04/19 112068

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/19 111352

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/19 83825

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79640

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 67004

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63128

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63067

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54097

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52219