Pag-unawa sa LFSC3GA25E-7F900C FPGA Architecture at Key Function

Ang paggalugad sa LFSC3GA25E-7F900C ay nagbibigay sa iyo ng mas malapitang pagtingin sa kung paano sinusuportahan ng mga programmable logic device ang mga flexible digital system.Maaari mong gamitin ang FPGA na ito upang ayusin ang mga path ng data, pamahalaan ang mga signal, at bumuo ng mga custom na function ng logic sa loob ng isang chip.Pinagsasama ng panloob na layout nito ang mga programmable logic cells, memory blocks, at input output banks para mahusay na gumagalaw ang mga signal sa device.Ang pag-unawa sa kung paano nagtutulungan ang mga seksyong ito ay nakakatulong sa iyong makita kung paano nakaayos ang mga kumplikadong electronic system.Mula sa hardware ng komunikasyon hanggang sa mga control system, ang FPGA na ito ay nag-aalok ng isang praktikal na paraan upang lumikha ng mga adaptable na digital na disenyo.Catalog

Pangkalahatang-ideya ng LFSC3GA25E-7F900C

LFSC3GA25E-7F900C ay isang programmable logic device na idinisenyo upang suportahan ang mga nako-configure na digital function sa mga naka-embed na electronic system.Ang device ay naglalaman ng grid based logic structure na may libu-libong mga programmable na elemento, internal memory resources, at maraming input at output na koneksyon para sa external na komunikasyon.Ang arkitektura nito ay nagpapahintulot sa mga digital circuit, control path, at mga gawain sa pagpoproseso ng signal na maipatupad sa loob ng isang chip.Ikinokonekta ng mga pinagsama-samang network ng pagruruta ang mga bloke ng lohika at mga seksyon ng memorya upang ang data ay makagalaw sa device sa isang nakabalangkas na paraan.Ang operasyon ay sinusuportahan ng isang mababang hanay ng supply ng core at isang mataas na pin count na package na angkop para sa mga siksik na layout ng board.

Naghahanap ng LFSC3GA25E-7F900C.Makipag-ugnayan sa amin para tingnan ang kasalukuyang stock, lead time, at pagpepresyo.

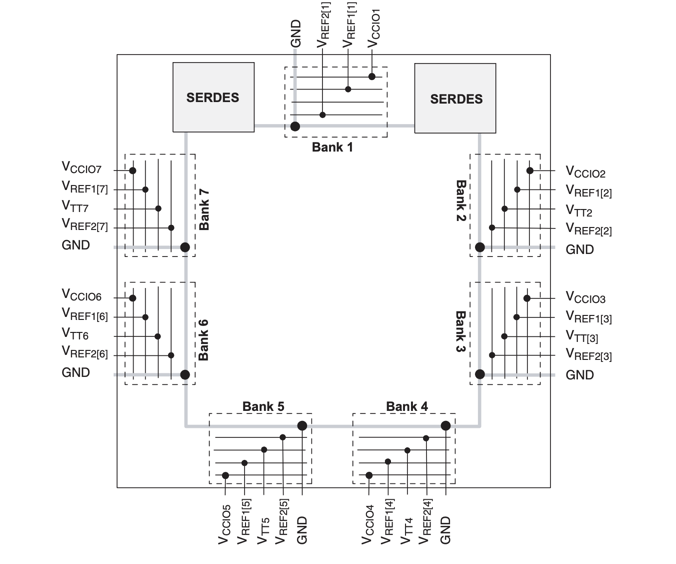

Mga bangko ng LFSC3GA25E-7F900C

Input at output bank arrangement na ginagamit sa LFSC3GA25E-7F900C FPGA na nagpapakita kung paano inaayos ng device ang mga programmable na mapagkukunan ng I O nito sa maraming mga rehiyon na kinokontrol ng boltahe.Ang walong bangko ay ipinamamahagi sa paligid ng perimeter ng device at ang bawat bangko ay may kasamang mga nakagrupong koneksyon para sa supply ng VCCIO, reference voltage input na may label na VREF, termination voltage pin na may label na VTT, at ground.Binibigyang-daan ng istrukturang ito ang bawat bangko na gumana nang may mga independiyenteng kundisyon ng kuryente upang masuportahan ang iba't ibang pamantayan ng signal sa magkahiwalay na panig ng device.Lumilitaw ang mga bloke ng interface ng SERDES malapit sa itaas na mga bangko upang suportahan ang mga high speed na serial communication channel na konektado sa mga kalapit na rehiyon ng I O.Tinutukoy din ng layout ang mga nakabahaging reference pin at power connections na tumutukoy kung paano nakikipag-ugnayan ang mga panlabas na signal sa internal programmable logic sa pamamagitan ng banked I O structure.

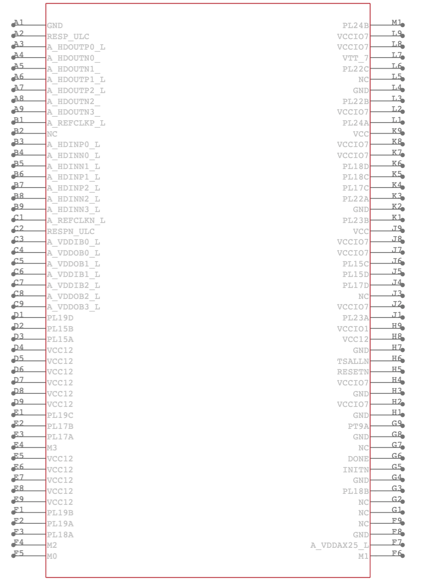

LFSC3GA25E-7F900C CAD na Modelo

Simbolo ng LFSC3GA25E-7F900C

LFSC3GA25E-7F900C Footprint

LFSC3GA25E-7F900C 3D na Modelo

Mga Tampok ng LFSC3GA25E-7F900C

High Density Programmable Logic

Ang aparato ay nagsasama ng humigit-kumulang dalawampu't limang libong mga programmable logic na elemento na nakaayos sa isang organisadong grid.Maaaring i-configure ang mga logic cell na ito para ipatupad ang mga digital control path, combinational logic, at arithmetic na operasyon sa loob ng mga naka-embed na system.

Naka-embed na Arkitektura ng Memorya

Ang mga mapagkukunan ng panloob na memorya ay nagbibigay ng higit sa isang megabit ng kapasidad ng imbakan para sa pag-buffer ng data at pagsuporta sa mga pagpapatakbo ng lohika.Ang mga bloke ng memorya na ito ay ipinamamahagi sa buong device upang ang mga logic circuit ay maaaring mag-access ng data nang lokal nang walang mahabang ruta sa pagruruta.

Flexible na Input At Output Connectivity

Hanggang tatlong daan at pitumpu't walong koneksyon sa input at output ang nagpapahintulot sa device na makipag-ugnayan sa mga sensor, mga interface ng komunikasyon, at iba pang mga digital na bahagi.Sinusuportahan ng istruktura ng pin ang maraming pamantayang elektrikal sa mga independiyenteng bangko ng I O.

Pinagsamang Mga Mapagkukunan sa Pamamahala ng Orasan

Ang mga panloob na bloke sa pamamahala ng orasan ay nakakatulong na ipamahagi ang mga signal ng timing sa buong programmable logic structure.Ang mga mapagkukunang ito ay nagpapanatili ng naka-synchronize na timing ng signal upang mangyari ang mga digital na operasyon sa isang maayos at predictable na pagkakasunud-sunod.

High Speed Serial Interface Capability

Sinusuportahan ng mga dedikadong serial interface block ang mga channel ng komunikasyon na may mataas na bilis para sa paglipat ng data sa pagitan ng mga module ng system.Ang mga bloke na ito ay kumokonekta sa kalapit na mga bangko ng I O at tumutulong na mapanatili ang matatag na paghahatid ng signal sa mga disenyong masinsinang data.

Structured Logic Processing Blocks

Pinapalawak ng mga dalubhasang internal processing block ang logic fabric at pinapayagan ang mga designer na ipatupad ang paulit-ulit na mga digital na istruktura nang mas mahusay.Sinusuportahan ng kaayusan na ito ang mga gawain tulad ng packet handling, control sequencing, at parallel data operations.

Programmable Routing Network

Ang isang structured routing network ay nagli-link ng mga logic cell, memory block, at interface pin.Maaaring maglakbay ang mga signal sa network sa maraming landas, na nagpapahintulot sa mga designer na ayusin ang mga digital na function sa mga paraan na tumutugma sa arkitektura ng system.

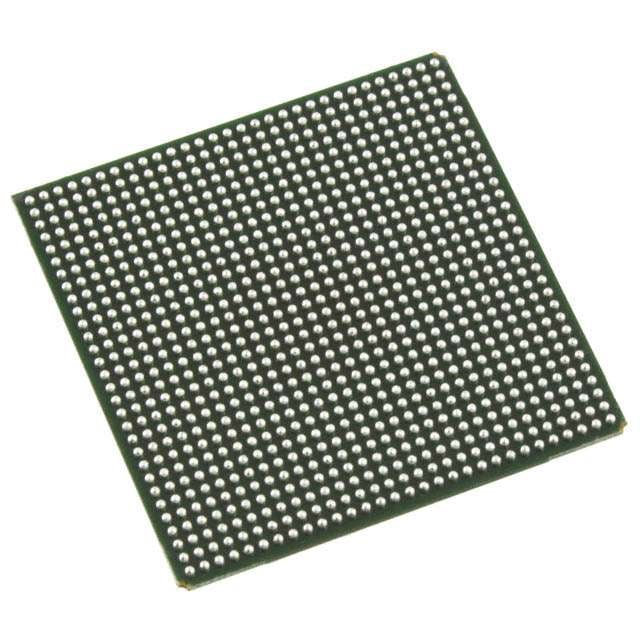

Pagsasama ng Surface Mount Package

Nakalagay ang device sa isang malaking ball grid array package na sumusuporta sa siksik na board integration.Ang istraktura ng package na ito ay nagbibigay-daan sa maraming mga de-koryenteng koneksyon na ayusin sa isang compact footprint para sa mga advanced na electronic assemblies.

LFSC3GA25E-7F900C Mga Teknikal na Detalye

| Katangian ng Produkto | Halaga ng Katangian |

| Manufacturer | Lattice Semiconductor |

| Boltahe - Supply | 0.95V ~ 1.26V |

| Kabuuang Mga Bit ng RAM | 1966080 |

| Package ng Supplier ng Device | 900-FPBGA (31x31) |

| Serye | SC |

| Package / Case | 900-BBGA |

| Package | Tray |

| Operating Temperatura | 0°C ~ 85°C (TJ) |

| Bilang ng Logic Elements/Cell | 25000 |

| Bilang ng mga LAB/CLB | 6250 |

| Bilang ng I/O | 378 |

| Uri ng Pag-mount | Ibabaw na Mount |

| Batayang Numero ng Produkto | LFSC3GA25 |

| Katayuan ng RoHS | Hindi sumusunod sa RoHS |

| Moisture Sensitivity Level (MSL) | 3 (168 Oras) |

| Katayuan ng REACH | REACH Hindi naaapektuhan |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

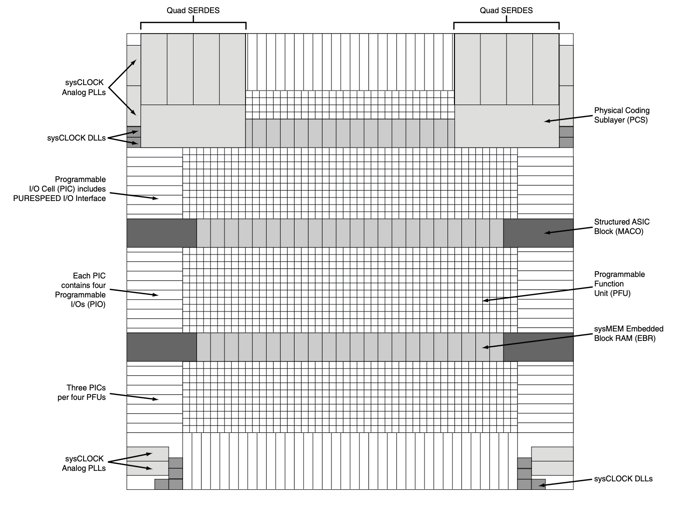

Pinasimpleng Block Diagram ng LFSC3GA25E-7F900C

Grid based na panloob na layout ng LFSC3GA25E-7F900C FPGA na nagpapakita ng pagsasaayos ng programmable logic, memory blocks, clock resources, at high speed interface structures.Binubuo ng mga programmable function unit ang central logic fabric kung saan ipinapatupad ang mga na-configure na digital circuit.Ang mga naka-distribute na sysMEM na naka-embed na block na mga seksyon ng RAM ay nagbibigay ng panloob na storage ng data at buffering sa loob ng logic array.Ang mga programmable na I O na cell na nakaposisyon sa mga gilid ng device ay kumokonekta sa panloob na logic sa mga panlabas na pin, sa bawat programmable na I O cluster na naglalaman ng maraming programmable na I O na koneksyon.Lumilitaw ang mga quad SERDES block at pisikal na coding sublayer interface malapit sa mga nangungunang rehiyon upang suportahan ang mataas na bilis ng serial communication.Ang mga istrukturang bloke ng ASIC na may label na MACO ay isinama sa loob ng tela ng lohika upang suportahan ang mga espesyal na istruktura ng pagproseso.Ang mga mapagkukunan sa pamamahala ng orasan na may label na sysCLOCK analog na PLL at sysCLOCK DLL ay inilalagay sa mga gilid ng layout upang bumuo at ipamahagi ang mga signal ng timing sa buong programmable na arkitektura.

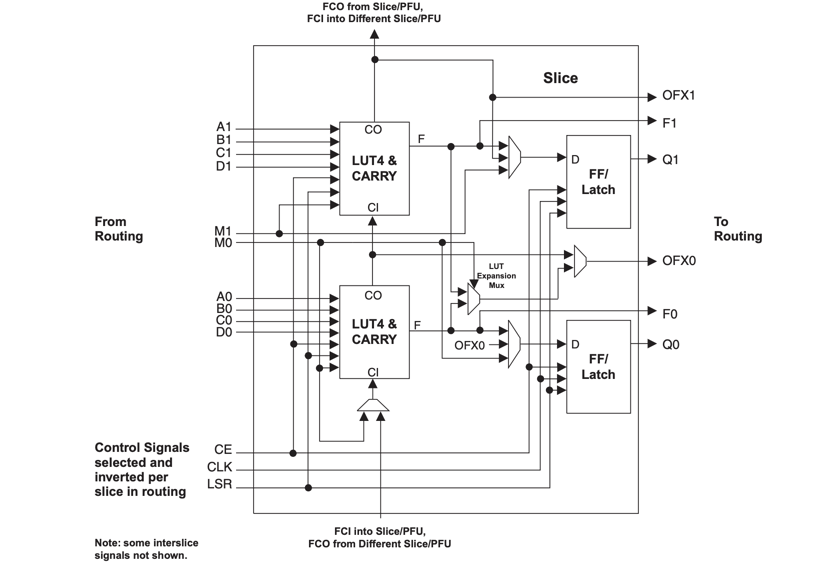

Slice Diagram ng LFSC3GA25E-7F900C

Panloob na istraktura ng isang logic slice na ginagamit sa loob ng programmable function unit ng LFSC3GA25E-7F900C FPGA.Dalawang bloke ng LUT4 ang gumaganap ng mga operasyong pang-kombinasyon na lohika gamit ang apat na signal ng input na may label na A, B, C, at D. Sinusuportahan ng pinagsamang carry logic ang mga operasyong aritmetika sa pamamagitan ng pag-uugnay ng carry input at pagdala ng mga signal ng output sa pagitan ng mga katabing hiwa.Ang mga elemento ng flip flop o latch ay nag-iimbak ng data ng output mula sa yugto ng lohika, na gumagawa ng mga nakarehistrong output na may label na Q0 at Q1.Ang mga control input tulad ng orasan, pag-enable ng orasan, at pag-set o pag-reset ng mga signal ay kinokontrol ang sequential operation ng mga elemento ng storage.Ang mga koneksyon sa pagruruta sa kaliwa at kanang mga gilid ay nagli-link sa slice sa nakapaligid na programmable interconnect network, na nagpapahintulot sa mga signal na pumasok mula sa mga mapagkukunan sa pagruruta at ibalik ang mga naprosesong output pabalik sa routing fabric.

Mga aplikasyon ng LFSC3GA25E-7F900C

Industrial Control System

Binibigyang-daan ng mga programmable logic resources ang device na pamahalaan ang mga sequence ng timing, pagruruta ng signal, at mga digital control na gawain sa automated na kagamitan.Maaari itong mag-coordinate ng maraming sensor at actuator habang pinapanatili ang matatag na digital processing sa loob ng control system.

Imprastraktura ng Komunikasyon ng Data

Ang mga kagamitan sa komunikasyon ay kadalasang nangangailangan ng nababaluktot na digital processing para sa paghawak ng data at kontrol sa interface.Maaaring iproseso ng device ang mga papasok na stream ng data, ayusin ang lohika ng pagruruta, at suportahan ang mga link ng komunikasyon sa loob ng hardware ng network.

Mga Naka-embed na Computing Platform

Gumagamit ang mga naka-embed na system ng programmable logic para pamahalaan ang daloy ng data sa pagitan ng mga processor, memory, at mga interface na device.Maaaring magpatupad ang device ng mga custom na digital path na umaangkop sa gawi ng system sa mga partikular na kinakailangan sa application.

High Speed Data Acquisition Systems

Ang mga sistema ng pagsukat ay madalas na nangongolekta ng mga signal mula sa maraming mapagkukunan nang sabay-sabay.Maaaring ayusin ng programmable logic structure ang mga papasok na digital signal, ihanay ang timing, at ihanda ang data para sa karagdagang pagproseso o paglilipat.

Hardware sa Pagproseso ng Signal

Maaaring ipatupad ng device ang mga na-configure na aritmetika at lohikal na operasyon na sumusuporta sa mga function sa pagpoproseso ng signal.Ang mga digital na filter, control loop, at mga gawain sa pagbabago ng data ay maaaring ipatupad nang direkta sa loob ng programmable logic structure.

LFSC3GA25E-7F900C Mga Kalamangan at Kahinaan

Mga kalamangan

• Malaking programmable logic capacity ay sumusuporta sa mga kumplikadong digital function

• Ang mataas na bilang ng mga koneksyon sa input at output ay nagbibigay-daan sa nababaluktot na pagsasama ng system

• Ang mga naka-embed na bloke ng memorya ay nagbibigay ng panloob na imbakan ng data at buffering

• Ang reconfigureable logic structure ay nagbibigay-daan sa mga function ng hardware na ma-update sa pamamagitan ng mga pagbabago sa disenyo

• Pinahihintulutan ng maraming I O na bangko ang iba't ibang pamantayan ng signal sa loob ng isang device

Mga disadvantages

• Ang proseso ng disenyo ay nangangailangan ng mga espesyal na tool sa pag-develop at mga daloy ng trabaho sa pagsasaayos

• Ang pagiging kumplikado ng device ay maaaring tumaas ang oras ng disenyo ng system sa panahon ng pag-develop

• Ang malaking sukat ng pakete ay nangangailangan ng maingat na layout ng naka-print na circuit board

• Dapat isaalang-alang ang pamamahala ng kapangyarihan kapag maraming mapagkukunan ng lohika ang aktibo

LFSC3GA25E-7F900C Mga Alternatibo

| Numero ng Bahagi | Manufacturer | Mga Pangunahing Tampok | Gamitin ang Case/Notes |

| LFSC3GA25E-7FFN1020C | Lattice Semiconductor Corporation | FPGA device mula sa pamilya ng SC na nag-aalok ng humigit-kumulang 25,000 logic elements, naka-embed na memory resources, at isang malaking bilang ng mga programmable I/O pin.Gumagamit ito ng fine pitch BGA package na sumusuporta sa mga dense circuit layout at kumplikadong digital na disenyo. | Ginagamit sa mga naka-embed na control system, mga interface ng komunikasyon, at pang-industriya na electronics kung saan kailangan ang programmable hardware at mataas na I/O connectivity. |

| LFSC3GA25E-7FFA1020C | Lattice Semiconductor Corporation | Programmable FPGA na may katulad na mga mapagkukunan ng lohika sa serye ng LFSC3GA25E.Nagbibigay ng mga configurable logic block, naka-embed na memory, at flexible na digital routing na nagbibigay-daan sa mga designer na magpatupad ng mga custom na digital circuit. | Angkop para sa digital signal processing, interface bridging, at programmable hardware control sa naka-embed na electronics at mga sistema ng komunikasyon. |

| LFSC3GA25E-6FN900C | Lattice Semiconductor Corporation | FPGA device na may humigit-kumulang 25K na elemento ng logic at pinagsama-samang mga bloke ng memorya na idinisenyo para sa programmable digital hardware.Nagbibigay ang package ng maraming koneksyon sa I/O na sumusuporta sa kumplikadong pagsasama ng system. | Kadalasang ginagamit sa mga pang-industriyang control system, mga naka-embed na computing platform, at networking equipment na nangangailangan ng flexible na configuration ng hardware. |

Tungkol sa Lattice Semiconductor

Ang Lattice Semiconductor ay isang kumpanya ng semiconductor na itinatag noong 1983 at naka-headquarter sa Hillsboro Oregon sa Estados Unidos.Bumubuo ang kumpanya ng mga programmable logic device at mga kaugnay na teknolohiya na ginagamit sa computing, komunikasyon, mga sistemang pang-industriya, at consumer electronics.Kasama sa mga linya ng produkto nito ang field programmable gate arrays, programmable logic device, at mga solusyon sa interface na idinisenyo upang suportahan ang flexible na disenyo ng digital system.Ang mga lattice device ay malawakang ginagamit sa mga naka-embed na system kung saan nakakatulong ang mga programmable na function ng hardware na pamahalaan ang pagpoproseso ng data, kontrolin ang lohika, at pagruruta ng signal sa loob ng mga compact na electronic platform.

Konklusyon

Pinagsasama ng LFSC3GA25E-7F900C FPGA ang programmable logic, naka-embed na memorya, at mga flexible input output na koneksyon sa loob ng isang device.Sa pamamagitan ng pag-unawa sa arkitektura nito, makikita mo kung paano nakaayos ang mga digital logic function at kung paano naglalakbay ang mga signal sa programmable fabric.Ang mga tampok tulad ng mga elemento ng configurable na logic, routing network, at clock management block ay nagbibigay-daan sa device na suportahan ang maraming disenyo ng system.Ginagawa nitong angkop ang istraktura nito para sa pagpoproseso ng data, kontrol na lohika, at hardware ng komunikasyon.Kapag ginalugad mo ang mga diagram at mga detalye, magkakaroon ka ng mas malinaw na larawan kung paano sinusuportahan ng programmable hardware ang mga adaptable na electronic system.

Datasheet PDF

Datasheet ng LFSC3GA25E-7F900C:

Lahat ng Dev Pkg Markahan Chg 12/Nov/2018.pdf

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Anong uri ng device ang LFSC3GA25E-7F900C?

Ang LFSC3GA25E-7F900C ay isang field programmable gate array, o FPGA, na nagbibigay-daan sa mga digital logic circuit na i-configure sa pamamagitan ng hardware programming.Naglalaman ito ng programmable logic blocks, routing resources, at mga elemento ng memorya sa loob ng isang chip.

2. Ano ang mga elemento ng lohika sa LFSC3GA25E-7F900C FPGA?

Ang mga elemento ng lohika ay maliit na programmable unit sa loob ng FPGA na magsagawa ng mga digital na operasyon tulad ng lohikal na paghahambing, arithmetic mga gawain, at pagproseso ng signal.Libu-libong mga elementong ito ang nagtutulungan upang lumikha ng mga custom na function ng hardware.

3. Paano gumagana ang I O mga bangko sa FPGA na ito?

Ang mga input output bank ay pangkat ng mga hanay ng mga pin na nagbabahagi ng kapangyarihan at reference mga boltahe.Ang bawat bangko ay maaaring suportahan ang iba't ibang mga pamantayang elektrikal, na nagbibigay-daan sa mga signal mula sa maraming interface na kumonekta sa parehong device.

4. Ano ang layunin ng naka-embed na memorya sa device?

Ang mga naka-embed na bloke ng memorya ay nag-iimbak ng data sa loob ng FPGA upang mag-logic circuit mabilis ma-access ang impormasyon.Ang mga bloke na ito ay ginagamit para sa buffering data, pansamantalang imbakan, at pagsuporta sa mga gawain sa pagpoproseso ng signal.

5. Saan karaniwang ginagamit ang LFSC3GA25E-7F900C?

Ang FPGA na ito ay karaniwang ginagamit sa mga sistema ng komunikasyon, pang-industriya control hardware, digital signal processing equipment, at naka-embed mga electronic platform kung saan kailangan ang programmable digital logic.

Ano ang Ginagawa ng EPF8282AVTC100-4 FPGA sa Digital System

sa 2026/03/10

Ano ang H7 na Baterya?Sukat, Mga Tampok, at Gamit ng Sasakyan

sa 2026/03/10

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147768

-

USB-C pinout at mga tampok

sa 2000/04/18 111996

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111351

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83758

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79555

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66955

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63098

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63029

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54095

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52176