Lahat ng kailangan mong malaman tungkol sa DDR3

Sa mabilis na umuusbong na mundo ng teknolohiya ng memorya, ang DDR3 SDRAM ay lumitaw bilang isang pagsulong sa groundbreaking, pagtugon sa pagtaas ng mga kahilingan para sa kahusayan, pagganap, at scalability sa modernong computing.Mula sa mga makabagong tampok tulad ng Command Writing Delay (CWD) at sa Die Calibration Engine (ODCE) sa mga kilalang pagpapahusay sa pamamahala ng kuryente at thermal control, ipinakilala ng DDR3 ang isang host ng mga kakayahan na muling tukuyin ang pagganap ng memorya.Ang artikulong ito ay galugarin ang mga pangunahing tampok, pagpapabuti ng arkitektura, at mga praktikal na aplikasyon ng DDR3, na nagpapagaan ng ilaw sa kung paano ito lumampas sa hinalinhan nito, DDR2, at nagtatakda ng isang bagong pamantayan sa disenyo ng memorya para sa parehong mga aplikasyon ng consumer at pang -industriya.Catalog

Pangkalahatang -ideya

Ang CWD, o pagkaantala sa pagsulat ng utos, ay isang mekanismo na idinisenyo upang ma -optimize ang mga pagkaantala sa pagsulat sa mga sistema ng memorya, pagpapahusay ng kahusayan sa pamamahala ng data.Ang utos ng pag-reset ay nagpapa-aktibo ng isang sobrang mode na naka-save ng lakas sa DDR3 SDRAM, huminto sa mga operasyon ng memorya at paglilipat ng system sa mababang enerhiya na standby.Ang tampok na ito ay nag -iingat ng enerhiya at nagpapalawak ng habang -buhay na memorya, ginagawa itong halos mahalaga para sa mga mobile at naka -embed na mga aplikasyon kung saan ginagamit ang kahusayan ng kuryente.

Ang pag-andar ng ZQ ay sumusulong sa pagkakalibrate ng paglaban sa terminal sa pamamagitan ng Die Calibration Engine (ODCE), Fine-Tuning on Die Pagwawakas (ODT) na pagtutol upang mapanatili ang integridad ng signal sa ilalim ng iba't ibang mga kondisyon.Ang pagkakalibrate na ito ay nagpapagaan ng mga panganib tulad ng pagkasira ng signal na maaaring makompromiso ang kawastuhan ng data at katatagan ng system.Ang mga kapaligiran sa pag-compute ng mataas na pagganap ay nagtatampok ng mga pagpapabuti ng pagiging maaasahan na ibinibigay ng mga pag-optimize na ito, lalo na sa mga aplikasyon na hinihingi ang pare-pareho na pagganap.

Ang pag-andar ng self-reflash temperatura (SRT) ay nagsasama ng programmable control control para sa kasalukuyang mga pagsasaayos sa bilis ng orasan ng memorya batay sa mga thermal kondisyon.Pinahuhusay nito ang pamamahala ng kuryente at pinipigilan ang sobrang pag -init, isang karaniwang hamon na maaaring humantong sa pag -throttling o pagkabigo sa sangkap.Bilang karagdagan, ang bahagyang array ng self-refresh (PASR) ay nagtatampok ng selectively refreshes aktibong mga segment ng memorya, na makabuluhang binabawasan ang pagkonsumo ng kuryente.Ang naka -target na diskarte sa pamamahala ng mapagkukunan ay malawak na kinikilala bilang isang epektibong diskarte para sa pag -optimize ng pagganap ng memorya nang hindi nagsasakripisyo ng kahusayan, karamihan sa mga system na may hindi regular na mga pattern ng paggamit ng memorya.

Bagong disenyo ng DDR3

Ang arkitektura ng memorya ng DDR3 ay nagpapakilala ng isang makabagong 8-bit na disenyo ng prefetch, na epektibong nagdodoble sa nakaraang 4-bit prefetch na katangian na matatagpuan sa DDR2.Ang pagsulong na ito ay nagbibigay -daan sa DRAM core na gumana sa 1/8 lamang ng dalas ng data.Halimbawa, ang DDR3-800 ay nagpapatakbo sa isang pangunahing dalas ng 100MHz, na nagpapakita ng isang makabuluhang paglukso sa kahusayan.

Ang mga pangunahing tampok ng disenyo na ito ay kinabibilangan ng:

• Ang pagpapatupad ng isang point-to-point topology, na makabuluhang binabawasan ang pag-load sa address, command, at control bus, na humahantong sa pinahusay na pangkalahatang pagganap ng system.

• Ang isang proseso ng pagmamanupaktura na bumaba sa ibaba 100nm, na nagreresulta sa pagbawas sa operating boltahe mula sa 1.8V sa DDR2 hanggang 1.5V.Ang pagbawas na ito ay hindi lamang nagtataguyod ng kahusayan ng enerhiya ngunit nagtataguyod din ng mas mahusay na pamamahala ng thermal sa loob ng system.

• Ang pagpapakilala ng mga asynchronous reset at pag -andar ng pag -calibrate ng ZQ, na nagmamarka ng isang makabuluhang pagbabagong -anyo sa disenyo na nagpapalakas ng katatagan at kahusayan sa pagpapatakbo.

Ang mga pagpapahusay na ito ay sumasalamin sa isang maalalahanin na diskarte sa arkitektura ng memorya, na naglalayong matugunan ang umuusbong na mga kahilingan ng modernong computing habang isinasaalang -alang ang mga aspeto tulad ng pagkonsumo ng enerhiya at pagganap ng system.

Paghahambing ng DDR2 at DDR3

|

Tampok |

DDR2 |

DDR3 |

|

Haba ng Burst (BL) |

Ang BL = 4 ay karaniwang ginagamit |

Ang BL = 8 ay naayos;Sinusuportahan ang isang 4-bit na pagsabog ng chop (BL = 4 basahin +

BL = 4 Sumulat sa Synthesize BL = 8).Kinokontrol sa pamamagitan ng linya ng address ng A12.Sumabog

Ang makagambala ay ipinagbabawal |

|

Pagtugon sa tiyempo |

Saklaw ng CL: 2-5;Karagdagang Latency (AL) Saklaw: 0–4

|

Saklaw ng CL: 5–11;Mga pagpipilian sa AL: 0, CL-1, CL-2.Nagdaragdag ng pagsulat

Pagkaantala (CWD) batay sa dalas ng operating |

|

I -reset ang pagpapaandar |

Hindi magagamit |

Bagong ipinakilala.Ang isang dedikadong pag -reset ng pin ay pinapasimple

Initialization, binabawasan ang pagkonsumo ng kuryente, at huminto sa mga panloob na pag -andar

sa panahon ng pag -reset |

|

Pag -calibrate ng ZQ |

Hindi magagamit |

Ipinakilala sa isang ZQ pin gamit ang isang sanggunian na 240-OHM

risistor.Awtomatikong i -calibrate ang output ng data at paglaban ng ODT |

|

Sanggunian ng sanggunian |

Solong sanggunian boltahe (VREF) |

Nahahati sa dalawang signal: vrefca (utos/address) at

VREFDQ (data bus), pagpapabuti ng ratio ng signal-to-ingay |

|

Koneksyon sa point-to-point (P2P) |

Maramihang mga channel ng memorya na suportado sa bawat controller |

Hinahawak ng Memory Controller ang isang channel na may isang puwang,

pagpapagana ng mga relasyon sa P2P o P22P.Binabawasan ang pag -load ng bus at nagpapabuti

Pagganap |

|

Pagkonsumo ng kuryente |

Pamantayang mekanismo ng self-refresh |

Mga advanced na tampok tulad ng awtomatikong self-refresh at bahagyang

Ang self-refresh batay sa temperatura, na humahantong sa mas mahusay na kahusayan |

|

Mga Aplikasyon |

Pangunahing ginagamit sa mga desktop at server |

Tamang -tama para sa mga mobile device, server, at desktop dahil sa

Mataas na dalas, bilis, at mas mababang pagkonsumo ng kuryente |

|

Suporta sa platform sa hinaharap |

Suportado sa mga sistema ng legacy at kasalukuyang mga platform |

Suportado ng Intel's Bear Lake at AMD K9 Platform para sa

Ang pagiging tugma sa hinaharap |

Mga pagpapabuti ng memorya ng DDR3

Lohikal na mga bangko

Ang ebolusyon mula sa DDR2 hanggang DDR3 ay kumakatawan sa isang kilalang shift in-memory architecture, na nagsisimula sa 8 lohikal na mga bangko at ang potensyal na mapalawak hanggang sa 16. Ang pag-unlad na ito ay lampas sa mga teknikal na pagpapahusay;Ito ay sumasalamin sa isang pagtaas ng demand para sa mga high-capacity chips na may kakayahang pangasiwaan ang mga kumplikadong aplikasyon.Habang ang parehong mga kinakailangan sa software at hardware ay patuloy na tumaas, ang kakayahang suportahan ang mas lohikal na mga bangko ay nagiging may kaugnayan.Ang mga karanasan sa iba't ibang mga industriya ay nagmumungkahi na ang mga sistema na idinisenyo na may scalability sa isip ay madalas na nagbibigay ng higit na pangmatagalang pagbabalik, dahil maaari silang ayusin sa mga pagbabago sa teknikal na hinaharap nang hindi nangangailangan ng malawak na overhaul.

Packaging

Ang DDR3 packaging ay nagpapahiwatig ng isang kamangha -manghang pagsulong sa engineering, na naka -highlight ng isang mas mataas na bilang ng pin na nagbibigay -daan sa mga bagong pag -andar.Ang paglipat mula sa 60/68/84-ball na FBGA packages ng DDR2 hanggang sa 78-ball FBGA para sa 8-bit chips at ang 96-ball FBGA para sa 16-bit chips ay naglalarawan ng paglukso na ito.Ang pagpapabuti na ito ay hindi lamang nagpapahusay ng mga kakayahan sa paglilipat ng data ngunit sumasalamin din sa isang lumalagong pangako sa pagpapanatili, dahil ang DDR3 ay sumusunod sa mahigpit na pamantayan sa kapaligiran, na nag -aalis ng mga nakakapinsalang sangkap.Sa landscape ng paggawa ngayon, maaari kang maging mas iginuhit sa mga produkto na unahin ang responsibilidad sa ekolohiya, na binibigyang diin ang pangangailangan na maghabi ng mga napapanatiling kasanayan sa mga makabagong ideya.

Pagkonsumo ng kuryente

Ang isang standout na tampok ng DDR3 ay ang kapasidad nito upang maihatid ang mataas na bandwidth habang makabuluhang binabawasan ang pagkonsumo ng kuryente.Sa pamamagitan ng pagbabawas ng boltahe ng operating mula sa 1.8V hanggang 1.5V ng DDR2, ang DDR3 ay inaasahang gumamit ng 30% na mas kaunting kapangyarihan sa pangkalahatan.Ang mga ratios ng kuryente para sa DDR3-800, 1066, at 1333-0.72x, 0.83x, at 0.95x ayon sa pagkakabanggit-ay nagtatayo ng isang malinaw na landas patungo sa pinahusay na pagganap at kahusayan.Ang pagbaba ng pagkonsumo ng kuryente ay hindi lamang sumusuporta sa pagpapanatili ng kapaligiran ngunit pinalawak din ang habang buhay ng aparato, dahil ang nabawasan na henerasyon ng init ay humahantong sa mas kaunting thermal stress sa mga sangkap.Ang makasaysayang data mula sa iba't ibang mga sektor ay nagpapahiwatig na ang mga teknolohiyang mahusay sa enerhiya ay may posibilidad na mas mababa ang mga gastos sa pagpapatakbo sa paglipas ng panahon, pinalakas ang halaga ng DDR3.

Mga kalamangan sa pagganap

|

Kalamangan sa pagganap |

Mga detalye |

|

Mas kaunting pagkonsumo ng kuryente at init |

Ang DDR3 ay kumukuha ng mga aralin mula sa DDR2, na binabawasan ang pagkonsumo ng enerhiya

at init habang pinapanatili ang kontrol sa gastos.Ginagawa nitong mas nakakaakit ang DDR3 sa iyo |

|

Mas mataas na dalas ng operating |

Dahil sa mas mababang pagkonsumo ng enerhiya, nakamit ng DDR3 ang mas mataas

mga frequency ng pagpapatakbo, pagbabayad para sa mas mahabang oras ng pagkaantala at nagsisilbing a

Nagbebenta ng point para sa mga graphic card |

|

Nabawasan ang gastos sa graphics card |

Gumagamit ang DDR3 ng mas malaking mga particle ng memorya (32m x 32-bit),

na nangangailangan ng mas kaunting mga chips upang makamit ang parehong kapasidad tulad ng DDR2, binabawasan ang PCB

lugar, pagkonsumo ng kuryente, at gastos |

|

Pinahusay na kakayahang magamit

|

Nag -aalok ang DDR3 ng mas mahusay na pagiging tugma sa DDR2 dahil sa

Hindi nagbabago ang mga pangunahing tampok (pin, packaging), na nagpapagana ng mas madaling pagsasama sa

umiiral na mga disenyo ng DDR2 |

|

Malawak na pag -aampon |

Ang DDR3 ay malawakang ginagamit sa mga bagong high-end graphics card at

lalong pinagtibay sa mga low-end graphics cards |

Kasaysayan ng Paglago

Ang pamantayang memorya ng DDR3, na opisyal na naipalabas ng JEDEC noong Hunyo 28, 2002, ay kumakatawan sa isang pangunahing sandali sa ebolusyon ng teknolohiya ng memorya.Gayunpaman, hindi hanggang 2006 na ang DDR2 ay tunay na nagsimulang mag -ukit ng angkop na lugar sa merkado.Ang lag na ito sa malawakang pagtanggap ay hindi humadlang sa mga tagagawa mula sa sabik na hinahabol ang mga solusyon sa DDR3, na nagtatampok ng isang pangitain na diskarte sa teknolohiya ng memorya na sa huli ay magbabago sa industriya.

PARA SA MARKET

Ang mga analyst ng merkado, kabilang ang mga mula sa ISuppli, ay inaasahan na noong 2008, ang DDR3 ay magtatatag ng isang nangingibabaw na posisyon sa loob ng sektor ng memorya, na nagtataya ng isang bahagi ng merkado na 55%.Sa pagtatapos ng 2008, ang mga module ng memorya ng DDR3, na nagpapatakbo sa mga dalas ng 1066, 1333, at 1600 MHz, ay madaling magamit sa mga mamimili.Habang ibinahagi ng DDR3 ang pagkakapareho ng arkitektura sa DDR2, epektibong tinapik nito ang mga pagkukulang ng hinalinhan nito, na pinadali ang isang makinis na paglipat at pagpapalakas ng mas malawak na pagtanggap.Ang pag -unlad na ito ay naglalarawan ng halaga ng kakayahang umangkop sa mga teknikal na pagsulong, dahil maaari mong matipid na tumugon sa mga pangangailangan ng mamimili habang sabay na pinapahusay ang mga sukatan ng pagganap.

Mga bagong tampok

Ang memorya ng DDR3 ay nagdudulot ng malaking pagpapahusay sa DDR2, na nagtatampok ng mga nakataas na rate ng paglipat ng data, isang makabagong topology para sa mga address at control bus, at pinahusay na kahusayan ng enerhiya.Ang pagpapakilala ng isang 8-bit na disenyo ng prefetch na sinamahan ng isang point-to-point na arkitektura ay hindi lamang na-optimize ang mga operasyon ngunit pinalalaki din ang pangkalahatang pagganap.Ang mga pagpapabuti na ito ay sumasalamin sa isang mas malawak na takbo sa teknolohiya kung saan ang bilis at kahusayan ay naghahari nang kataas -taasan.Ang mga pananaw mula sa iba't ibang mga sektor ay nagpapakita na ang mga taong yumakap sa pagbabago ay madalas na nag -secure ng isang mapagkumpitensyang gilid, na napatunayan ng mabilis na pag -ampon ng DDR3 sa maraming mga aplikasyon.

Milestone ng kapasidad

Sa huling bahagi ng 2009, nakuha ng Samsung ang pansin sa pagpapalabas ng isang groundbreaking 4GB DDR3 chip na gawa sa paggamit ng isang 50nm na proseso, na nagpapagana ng paglikha ng 32GB memory sticks at makabuluhang pagpapahusay ng potensyal ng 64-bit na computing.Ipinagmamalaki din ng chip na ito ang isang kahanga -hangang 40% na pagbawas sa pagkonsumo ng kuryente kumpara sa mga naunang henerasyon.Ang mga projection na nagpapahiwatig ng pagtaas ng pagbabahagi ng merkado ng DDR3 sa 72% noong 2011 ay higit na nagpakilala sa natural na pag -unlad mula sa DDR2 hanggang DDR3.Ang pagbabagong ito ay nagsisilbing isang paalala ng siklo ng kalikasan ng pagsulong ng teknolohiya, kung saan ang bawat bagong pag-ulit ay nagtatayo sa hinalinhan nito, pagmamaneho ng pagbabago at kahusayan sa isang nagbabago na digital na kapaligiran.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Pagproseso ng Digital Signal: Mga Prinsipyo at Aplikasyon

sa 2024/12/30

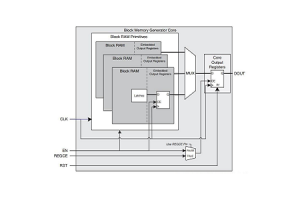

Paggalugad ng block ram sa serye ng Xilinx SP3: Mga Tampok, Pagkakaiba, at Pag -optimize

sa 2024/12/30

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147757

-

USB-C pinout at mga tampok

sa 2000/04/18 111936

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111349

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83721

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79508

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66905

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63034

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63012

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54081

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52125