Pagpapahusay ng disenyo ng FPGA na may mga file ng pagpilit ng gumagamit (UCF) para sa mga tool ng Xilinx ISE

Ang gabay na ito ay galugarin ang papel ng mga file ng pagpilit ng gumagamit (UCFS) sa pagpapabuti ng disenyo ng FPGA na may mga tool sa Xilinx ISE.Pinapayagan ng mga UCF na magdagdag ng mga tukoy na hadlang upang mas mahusay na kontrolin ang tiyempo, lohika, at paglalagay, na nagpapalakas ng kawastuhan ng disenyo, pagganap, at pagiging maaasahan.Sa pamamagitan ng pagpapakita kung paano mailalapat nang epektibo ang mga hadlang na ito, ang gabay ay tumutulong na gawing simple ang proseso ng disenyo, gupitin ang oras ng pag -debug, at matiyak ang matagumpay na paghahatid ng proyekto.Catalog

Layunin at papel ng UCFS sa disenyo ng FPGA

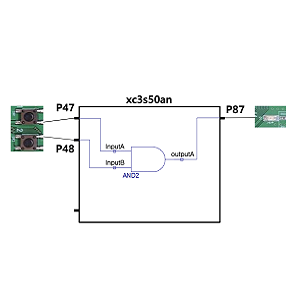

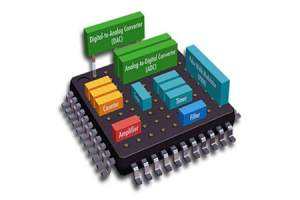

Sa disenyo ng FPGA, ang mga file ng pagpilit ng gumagamit (UCFS) ay gumaganap ng isang papel sa pagkontrol kung paano ang lohika na synthesized mula sa iyong code ay nakakakuha ng pisikal na ipinatupad sa chip.Hinahayaan ng mga file na ito na tukuyin ang mga mahahalagang parameter tulad ng mga hadlang sa tiyempo, mga asignatura sa PIN, at mga detalye ng paglalagay ng lugar na maaaring direktang makakaapekto kung ang isang disenyo ay nakakatugon sa mga kinakailangan sa pagganap o hindi.Mag -isip ng mga UCF bilang mga blueprints na matiyak na ang lahat ay nakaposisyon nang tama, gumagana sa iskedyul, at maayos na umaangkop sa lugar.Ang proseso ng setting ng pagpilit ay nagsisimula sa mga unang yugto ng pag -unlad.Magsimula sa pamamagitan ng paglikha ng isang UCF file bago ang synthesis, tinitiyak na ang mga parameter ay naka -lock sa kanan mula sa simula.Matapos ang synthesis, ang mga karagdagang mga file ng pagpilit tulad ng NetList Constraint File (NCF) at Physical Constraint File (PCF) ay nabuo upang ipakita ang mga pagbabago na ginawa sa lohika at upang tapusin ang mga pisikal na hadlang.Ang bawat isa sa mga file na ito ay bumubuo sa nakaraang hakbang, na unti -unting pinino ang disenyo.Ang mga UCF ay mga file na batay sa teksto na nakasulat sa format na ASCII, na nangangahulugang maaari silang mai-edit gamit ang mga pangunahing editor ng teksto o mas dalubhasang mga tool tulad ng Xilinx Constraint Editor.Ang pagiging simple na ito ay ginagawang lubos na naa -access at nababaluktot ang UCFS upang sumisid sa mga detalye ng mga setting ng pagpilit nang hindi nangangailangan ng labis na kumplikadong mga tool.

Paano hadlang ang hugis ng disenyo ng FPGA?

Sa disenyo ng FPGA, ang mga hadlang ay may papel sa paghubog kung paano gumaganap ang chip at nakikipag -ugnay sa mga panlabas na aparato.Ang mga hadlang na ito ay tinukoy sa isang UCF (User Constraints File), na kumikilos bilang isang detalyadong pagtuturo na itinakda para sa tool ng disenyo, na tinukoy kung paano ang mga panloob na sangkap ng FPGA ay dapat na konektado at pinamamahalaan.Kasama sa mga pangunahing hadlang ang mga hadlang sa tiyempo, na matiyak na ang mga senyas ay naglalakbay sa pagitan ng mga sangkap sa loob ng isang tiyak na frame ng oras upang mapanatili ang maaasahang pagganap sa nais na bilis ng orasan.Ang mga takdang aralin ay mapa ang mga pisikal na pin ng FPGA sa mga panlabas na aparato tulad ng mga sensor, mga module ng memorya, o mga interface ng komunikasyon, tinitiyak ang tumpak na mga koneksyon.Kinokontrol ng mga hadlang sa lugar ang paglalagay ng mga bloke ng lohika sa chip upang maiwasan ang kasikipan, bawasan ang mga pagkaantala, at i -optimize ang paggamit ng mapagkukunan.Kung wala ang mga hadlang na ito, ang mga awtomatikong tool ay gagawa ng mga desisyon sa paglalagay at pagruruta, ngunit madalas na may mga resulta ng suboptimal, na humahantong sa mga isyu sa tiyempo, mga bottlenecks, o hindi mahusay na mga layout ng chip.Sa pamamagitan ng paggamit ng mga file ng UCF, marami ang nagpapanatili ng kontrol sa mga kritikal na aspeto na ito, na nagreresulta sa mas mahusay na pagganap, kahusayan, at pagiging maaasahan sa mga disenyo ng FPGA.

Ang iterative na kalikasan ng pagpapagaan ng pagpipino

Ang disenyo ng FPGA ay bihirang isang proseso ng isang-at-tapos na.Ang mga hadlang ay paulit -ulit na nababagay sa buong pag -unlad ng pag -unlad habang lumilitaw ang disenyo at lumitaw ang mga bagong hamon.Ang iba ay nag -tweak ng mga file ng UCF upang matugunan ang mga target ng pagganap, ayusin ang mga isyu sa tiyempo, o umangkop sa pagbabago ng mga kinakailangan sa proyekto.Ang iterative refinement na ito ay isang mahalagang bahagi ng FPGA workflow.Halimbawa, kung napansin mo na ang isang landas ng signal ay tumatagal ng masyadong mahaba upang magpalaganap sa pagitan ng dalawang sangkap, maaari nilang baguhin ang UCF upang mabago ang pagpilit sa tiyempo o ilipat ang mga sangkap na iyon upang mabawasan ang mga pagkaantala.Katulad nito, kung ang isang pagtatalaga sa PIN ay salungatan sa panlabas na hardware, ang UCF ay maaaring mai -edit upang malutas ang mismatch.Ang bawat rebisyon ng UCF ay gumagalaw sa disenyo na mas malapit sa nais na kinalabasan, na ang bawat pagsasaayos ay nagtuturo nang higit pa tungkol sa mga trade-off na kasangkot sa pag-optimize ng FPGA.Ang siklo ng pagsubok, pag -aayos, at pag -aaral ay hindi lamang nagpapabuti sa disenyo ngunit din ang mga kasanayan sa mga kasanayan.

Mga Pakinabang ng Paggamit ng UCFS

Ang paglalapat ng mga hadlang sa pamamagitan ng mga file ng UCF ay nagbibigay ng maraming mga praktikal na pakinabang na nag -aambag sa tagumpay ng mga proyekto ng FPGA:

• Pinahusay na katumpakan ng tiyempo: mahusay na ginawa na mga hadlang sa tiyempo matiyak na ang FPGA ay nagpapatakbo ng maaasahan sa nais na bilis ng orasan, pag-iwas sa mga pagkakamali na dulot ng mga pagkaantala ng signal.

• Mas mahusay na paggamit ng mapagkukunan: Pinipigilan ng mga hadlang sa lugar ang mga bloke ng lohika na mailagay masyadong malapit o masyadong malayo, na -optimize ang puwang ng chip at pagpapabuti ng pagganap.

• Ang pinasimple na pag -debug: Sa pamamagitan ng pagkontrol sa mga takdang -PIN at pag -ruta ng signal, ang mga UCF ay tumutulong na mabawasan ang mga salungatan sa pagruruta, na ginagawang mas madali ang pag -diagnose at ayusin ang mga isyu sa panahon ng pagsubok.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Mga Pamantayang Pamantayang Pamantayan ng Application (ASSP): Pagmamaneho ng Pagmamaneho sa Modernong Elektronika

sa 2025/01/8

System sa isang Programmable Chip (SOPC): Teknolohiya, Disenyo, at Mga Aplikasyon

sa 2025/01/8

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147768

-

USB-C pinout at mga tampok

sa 2000/04/18 111996

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111351

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83759

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79555

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66955

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63098

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63029

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54095

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52176