EP1C4F400C8 FPGA: Mga Tampok, Mga Pagtukoy, Programming at Alternatibo

Kung nagtatrabaho ka sa programmable logic, binibigyan ka ng EP1C4F400C8 ng isang praktikal na balanse ng pagganap at gastos.Sa artikulong ito, malalaman mo kung ano ang FPGA na ito, ang mga pangunahing tampok nito tulad ng Logic Capacity, Memory, at mga pagpipilian sa I/O, at kung paano sinusuportahan ng istraktura ang maaasahang disenyo.Makikita mo rin ang mga pagtutukoy nito, mga aplikasyon sa mga system, proseso ng pagprograma, at kung paano ito inihahambing sa mga katulad na bahagi.Catalog

Ano ang EP1C4F400C8?

Ang EP1C4F400C8 ay isang miyembro ng Intel's (dating Altera's) Cyclone FPGA Family, na idinisenyo bilang isang epektibo at maaasahang ma-program na solusyon sa lohika.Itinayo sa isang proseso ng 0.13 µM SRAM, ang aparatong ito ay nag-aalok ng katamtamang logic density at nababaluktot na mga pagpipilian sa I/O sa loob ng isang compact na FBGA-400 package.Ang pamilya ng bagyo, na kinabibilangan ng mga aparato tulad ng EP1C3, EP1C6, EP1C12, at EP1C20, ay nilikha upang balansehin ang pagganap at kakayahang magamit para sa mga nasusukat na disenyo, na nagpapahintulot sa madaling paglipat sa pagitan ng mga antas ng density at mga pakete.Kilala sa katatagan at malawak na pag -aampon, nananatili itong isang mapagkakatiwalaang pagpipilian sa mga disenyo ng legacy.

Naghahanap ng EP1C4F400C8?Makipag -ugnay sa amin upang suriin ang kasalukuyang stock, oras ng tingga, at pagpepresyo.

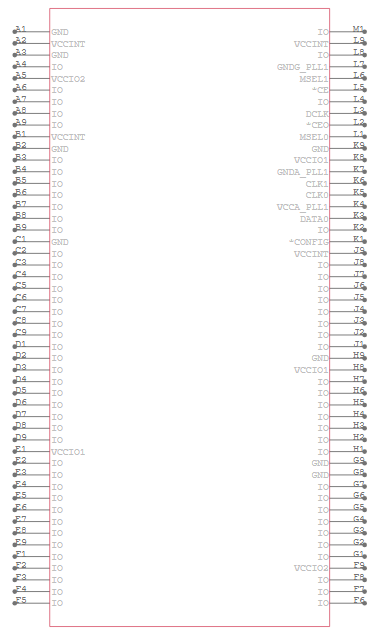

Mga modelo ng EP1C4F400C8 CAD

Simbolo ng EP1C4F400C8

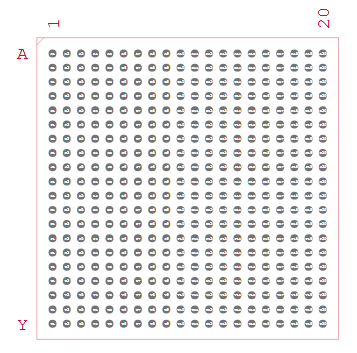

EP1C4F400C8 Footprint

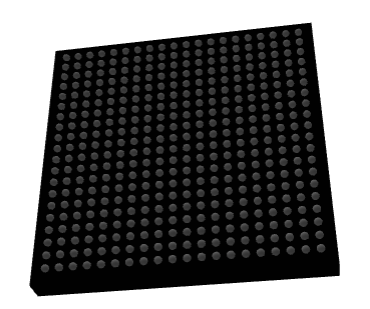

EP1C4F400C8 3D Model

Mga tampok ng EP1C4F400C8

At Kapasidad ng lohika

Nag -aalok ang EP1C4F400C8 sa paligid ng 4,000 mga elemento ng lohika, na naayos sa 400 na mga bloke ng logic array (lab).Ginagawa nitong angkop para sa mga disenyo ng mid-range na nangangailangan ng katamtamang density ng lohika habang pinapanatili ang kahusayan ng gastos.

At Naka -embed na memorya

Isinasama nito ang humigit -kumulang na 76.5 kbits ng naka -embed na memorya.Sinusuportahan ng panloob na RAM na ang data buffering, imbakan, at maliit na pag -andar ng memorya, binabawasan ang pangangailangan para sa mga panlabas na sangkap ng memorya sa maraming mga disenyo.

At Mataas na bilang ko

Nagbibigay ang aparato ng 301 user-configure I/O pin sa 400-ball na FBGA package.Ang mataas na bilang ng pin na ito ay nagbibigay -daan sa mayaman na koneksyon para sa mga kumplikadong sistema na nangangailangan ng maraming mga interface ng peripheral.

At Malawak na suporta sa I/O Standards

Sinusuportahan nito ang maraming mga pamantayan sa I/O kabilang ang LVTTL, LVCMOS, SSTL-2, SSTL-3, at pagkakaiba-iba ng mga LVD.Ang kakayahang umangkop na ito ay nagbibigay -daan sa FPGA na makipag -ugnay nang direkta sa iba't ibang mga modernong pamilya ng lohika at mga aparato ng memorya.

At High-speed kaugalian signaling

Sa suporta ng LVD hanggang sa 640 Mbps, ang FPGA ay humahawak ng mabilis na mga kinakailangan sa paglilipat ng data.Ginagawa nitong praktikal para sa mga aplikasyon tulad ng mga link na may mataas na bilis ng komunikasyon at mabilis na mga interface ng digital.

At Pamamahala ng orasan na may mga PLL

Ang chip ay nagsasama ng dalawang phase-lock loops (PLL) at walong pandaigdigang network ng orasan.Pinapayagan ng mga tampok na ito ang tumpak na henerasyon ng orasan, pagdami, at kontrol ng jitter para sa mga aplikasyon ng kritikal na tiyempo.

At Ang operasyon ng mababang boltahe

Ang pagpapatakbo sa isang nominal na 1.5 V core boltahe, binabalanse ng aparato ang pagganap na may mas mababang pagkonsumo ng kuryente.Ang antas ng boltahe na ito ay na-optimize para sa teknolohiyang 0.13-µM CMOS na ginamit sa katha nito.

At Flexible I/O Voltages

Sinusuportahan ng FPGA ang I/O boltahe ng 1.5 V, 1.8 V, 2.5 V, at 3.3 V sa iba't ibang mga bangko.Ang kakayahang umangkop na ito ay nagbibigay -daan sa pakikipag -ugnay sa parehong mga sangkap ng legacy at modernong system.

At Ang pagsasaayos na batay sa SRAM

Tulad ng iba pang mga bagyo na FPGA, ito ay batay sa SRAM at nangangailangan ng muling pagsasaayos sa bawat power-up.Nagbibigay ito ng kakayahang umangkop para sa mga pag -update ngunit nangangailangan din ng isang panlabas na aparato ng pagsasaayos o magsusupil.

At Suporta sa compression ng Bitstream

Sinusuportahan ng EP1C4F400C8 ang mga naka -compress na pag -load ng bitstream sa panahon ng pagsasaayos.Binabawasan nito ang mga panlabas na kinakailangan sa memorya at pinapabilis ang mga oras ng pagsasaayos.

At Pagsunod sa PCI

Kasama dito ang built-in na suporta para sa mga pamantayan sa PCI (33/66 MHz, 32/64-bit).Pinapayagan ng tampok na ito ang aparato na direktang isinama sa mga system na nangangailangan ng interface ng PCI nang walang karagdagang logic ng bridging.

Istraktura ng bag ng bagyo

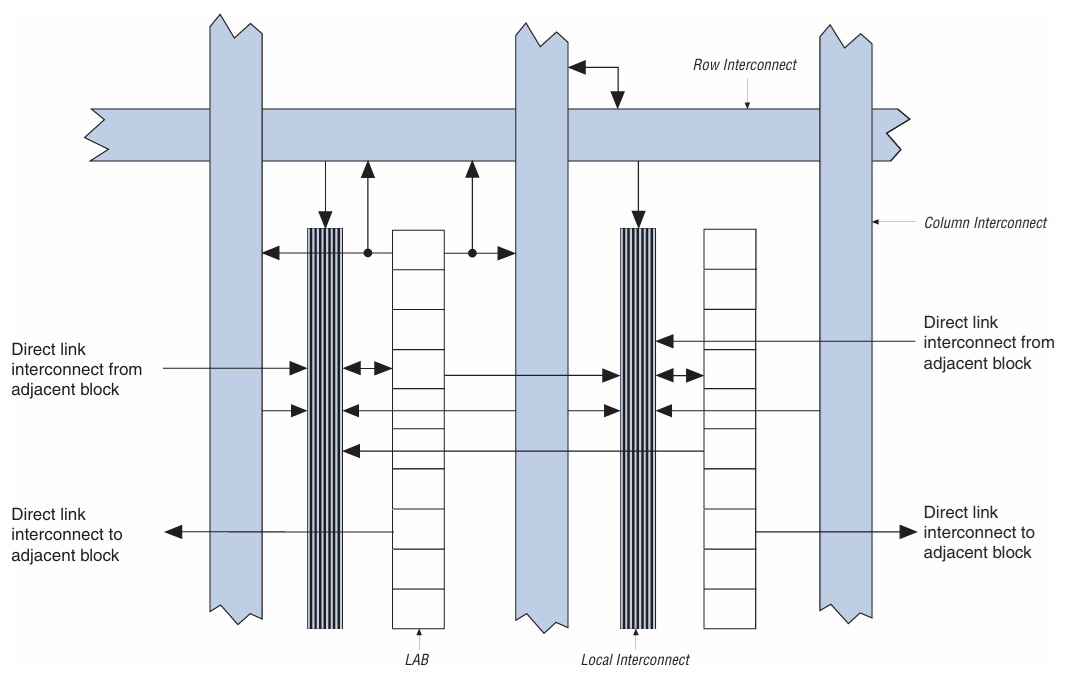

Ipinapakita ng diagram ang istraktura ng logic array block (LAB) na ginamit sa cyclone fPGA tulad ng EP1C4F400C8.Ang bawat lab ay kumokonekta sa isang network ng mga magkakaugnay: mga magkakaugnay na hilera, mga magkakaugnay na haligi, at mga lokal na magkakaugnay, na kung saan ang mga signal ng ruta sa pagitan ng mga elemento ng lohika at iba pang mga bloke.Ang mga direktang link na magkakaugnay ay nagbibigay ng mabilis, mababang-latency na mga landas sa katabing mga lab, pagpapabuti ng pagganap ng tiyempo sa mga landas ng signal.Mahalaga ang arkitektura na ito sapagkat binabalanse nito ang pag -ruta ng kakayahang umangkop na may kahusayan, na nagpapagana sa FPGA na hawakan ang mga kumplikadong disenyo habang pinapanatili ang bilis at lugar na na -optimize.

Cyclone I/O Banks diagram

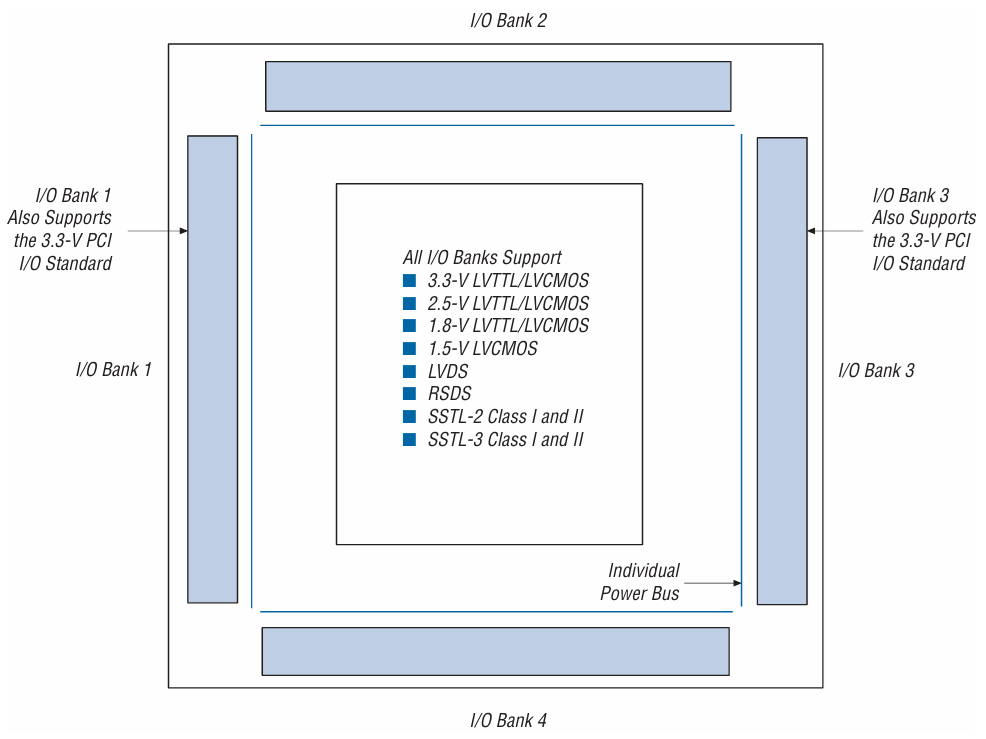

Inilalarawan ng diagram ang istruktura ng I/O Bank ng mga bagyo na FPGA tulad ng EP1C4F400C8.Ang aparato ay nahahati sa apat na mga bangko ng I/O, ang bawat isa ay pinalakas ng sarili nitong supply bus, na nagpapahintulot na maghalo ng iba't ibang mga pamantayan sa boltahe sa loob ng isang FPGA.Ang lahat ng mga bangko ay sumusuporta sa isang malawak na hanay ng mga pamantayan ng I/O kabilang ang LVTTL, LVCMOS, LVDS, RSDS, at SSTL, habang ang mga bangko 1 at 3 ay sumusuporta din sa 3.3-V PCI para sa pagiging tugma sa mga sistema ng legacy.Mahalaga ang kakayahang umangkop na I/O na arkitektura dahil pinapayagan nito ang walang tahi na pagsasama sa magkakaibang mga panlabas na aparato at interface, na ginagawang naaangkop ang FPGA sa iba't ibang mga aplikasyon.

Mga pagtutukoy ng EP1C4F400C8

|

I -type |

Parameter |

|

Tagagawa |

Altera/Intel |

|

Serye |

Cyclone® |

|

Packaging |

Tray |

|

Bahagi ng Bahagi |

Lipas na |

|

Bilang ng mga lab/clbs |

400 |

|

Bilang ng mga elemento/cell ng lohika |

4000 |

|

Kabuuang mga ram bits |

78,336 |

|

Bilang ng I/O. |

301 |

|

Boltahe - Supply |

1.425V ~ 1.575V |

|

Uri ng pag -mount |

Surface Mount |

|

Temperatura ng pagpapatakbo |

0 ° C ~ 85 ° C (TJ) |

|

Package / Kaso |

400-BGA |

|

Package ng aparato ng supplier |

400-FBGA (21 × 21) |

|

Base Number Product |

EP1C4 |

Mga Application ng EP1C4F400C8

1. Pagproseso ng Digital Signal (DSP)

Ang EP1C4F400C8 ay maaaring ma -program upang maisagawa ang mga gawain tulad ng pag -filter, FFTS, at modulation ng signal.Ang kumbinasyon ng mga elemento ng lohika at naka-embed na memorya ay ginagawang angkop para sa pagproseso ng high-speed.Pinapayagan nito na palitan ang tradisyonal na mga chips ng DSP na may isang nababaluktot na solusyon sa FPGA na maaaring ma -reprogrammed para sa iba't ibang mga algorithm.

2. Mga naka -embed at control system

Sa mga sistemang pang -industriya at naka -embed, ang FPGA na ito ay madalas na ginagamit upang ipatupad ang mga pasadyang mga controller, sequencer, at mga makina ng estado.Ang muling mai -configure na lohika ay nagbibigay -daan upang maiangkop ang pag -uugali ng hardware nang tumpak sa mga pangangailangan ng system.Sa pamamagitan ng pagsasama ng control logic sa loob ng FPGA, ang bilang ng mga panlabas na sangkap ay nabawasan, pagpapabuti ng pagiging maaasahan at pagbaba ng gastos.

3. Komunikasyon at interface bridging

Sinusuportahan ng aparato ang maraming mga pamantayan sa I/O at maaaring kumilos bilang isang tulay sa pagitan ng iba't ibang mga protocol ng komunikasyon.Madalas itong ginagamit upang ikonekta ang PCI, LVD, SDRAM, at iba pang mga interface nang walang putol sa loob ng isang system.Ginagawa nitong lubos na kapaki-pakinabang sa mga kagamitan sa networking, naka-embed na mga magsusupil, at mga conversion ng legacy-to-modern interface.

4. Pagkuha ng Data at Pagproseso

Sa mataas na memorya ng I/O at nababaluktot na memorya, ang EP1C4F400C8 ay angkop para sa mga sistema ng pagkolekta ng data.Maaari itong direktang makipag -ugnay sa mga ADC at sensor, iproseso ang data sa oras, at ihanda ito para sa imbakan o paghahatid.Ang mga nasabing aplikasyon ay karaniwan sa mga medikal na instrumento, kagamitan sa pagsubok, at mga aparato sa pagsukat ng pang -agham.

Ang mga katulad na bahagi ng EP1C4F400C8

|

Pagtukoy |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Tagagawa |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Pamilya ng FPGA |

Bagyo (EP1C4) |

Bagyo (EP1C4) |

Bagyo (EP1C4) |

Bagyo (EP1C4) |

Bagyo (EP1C4) |

Bagyo (EP1C4) |

|

Mga elemento ng lohika (LES) |

4,000 |

4,000 |

4,000 |

4,000 |

4,000 |

4,000 |

|

Naka -embed na memorya (bits) |

~ 76.5 kbits |

~ 76.5 kbits |

~ 76.5 kbits |

~ 76.5 kbits |

~ 76.5 kbits |

~ 76.5 kbits |

|

I/o pin |

301 |

301 |

301 |

301 |

249 |

97 |

|

Package / Kaso |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-tqfp |

|

Bilis ng grado |

C8 |

C8 |

C8 |

C6 (mas mabilis) |

C8 |

C8 |

|

Pangunahing boltahe |

1.5 v |

1.5 v |

1.5 v |

1.5 v |

1.5 v |

1.5 v |

|

Operating temp.Saklaw |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 Mga Hakbang sa Programming

Bago mo magamit ang EP1C4F400C8 FPGA, dapat mong i -load ang iyong disenyo sa aparato.Ang Programming ay nagsasangkot ng pag -configure ng FPGA na may isang file ng bitstream upang malaman nito kung paano kumilos bilang iyong inilaan na circuit.

1. Piliin ang Scheme ng Pag -configure at Itakda ang Mga Pins ng MSEL

Nagsisimula ka sa pamamagitan ng pagpili ng scheme ng pagsasaayos na pinakamahusay na umaangkop sa iyong pag -setup, tulad ng aktibong serial, passive serial, o JTAG.Ginagawa ito sa pamamagitan ng pagtatakda ng mga pin ng MSEL sa mga tiyak na antas ng lohika bago ang power-up.Ang bawat mode ay gumagamit ng iba't ibang mga pin at protocol, kaya kailangan mong kumpirmahin ang pagiging tugma sa iyong mga tool sa disenyo at memorya ng pagsasaayos.Ang paggawa ng tamang pagpipilian dito ay nagsisiguro ng isang maayos na proseso ng pagsasaayos.

2. Mag -apply ng kapangyarihan at simulan ang aparato

Susunod, pinapagana ang core ng FPGA at I/O na mga riles sa loob ng tinukoy na saklaw ng boltahe.Sa panahon ng pagsisimula, panatilihing mababa ang NConfig PIN upang hawakan ang aparato upang mai -reset hanggang matatag ang mga boltahe ng supply.Kapag matatag, pinakawalan mo ang pag -reset at ang aparato ay nagpapahiwatig ng pagiging handa sa pamamagitan ng pagmamaneho ng NSTATUS pin.Ginagarantiyahan nito ang FPGA ay maayos na sinimulan bago magsimula ang pagsasaayos.

3. Ipadala ang pagsasaayos ng bitstream

Sa yugtong ito, ipinapadala mo ang file ng data ng pagsasaayos (bitstream) sa FPGA gamit ang iyong napiling scheme.Sa aktibong serial o passive serial mode, ang bitstream ay nagmula sa isang panlabas na aparato ng memorya, habang pinapayagan ng JTAG ang direktang programming sa pamamagitan ng cable.Patuloy na binabasa ng aparato ang data ng pagsasaayos hanggang sa makumpleto ito.Ang iyong disenyo ng software ay bumubuo ng bitstream na ito upang tumugma sa iyong mga kinakailangan sa lohika.

4. Kumpirmahin ang matagumpay na pagsasaayos (conf_done)

Kapag natapos ang FPGA na naglo -load, iginiit nito ang conf_done pin upang ipakita na ang data ng pagsasaayos ay matagumpay na natanggap.Kasabay nito, ang aparato ay nagsasagawa ng panloob na pagsisimula tulad ng pag -clear ng mga rehistro at pag -activate ng I/O.Kung nabigo ang conf_done na tumaas, karaniwang nangangahulugang ang data ng pagsasaayos o pag -setup ay may error.Ang panonood ng pin na ito ay ang pinakasimpleng paraan upang mapatunayan ang proseso ay kumpleto.

5. Magsagawa ng opsyonal na pag-configure ng in-system

Sa wakas, mayroon kang pagpipilian upang i -update o i -reprogram ang FPGA nang hindi tinanggal ito sa board.Gamit ang JTAG o isang naka -embed na magsusupil, maaari kang mag -load ng isang bagong bitstream nang direkta, na kapaki -pakinabang para sa mga pag -update ng firmware.Ang kakayahang umangkop na ito ay nagbibigay -daan sa iyo upang baguhin, i -debug, o i -upgrade ang iyong system kahit na pagkatapos ng pag -deploy.Tinitiyak nito ang iyong disenyo na batay sa FPGA ay maaaring umangkop sa paglipas ng panahon sa pagbabago ng mga kinakailangan.

EP1C4F400C8 Mga kalamangan at Kakulangan

Kalamangan

• Pagpipilian sa mahusay na gastos para sa mga disenyo ng mid-range

• Mataas na bilang ng I/O kumpara sa mga katulad na aparato ng density

• Flexible boltahe at pamantayang suporta sa I/O.

• Nai -back sa pamamagitan ng mga mature na tool at dokumentasyon

• Ang mas mababang paggamit ng kapangyarihan kaysa sa mga mas matatandang henerasyon ng FPGA

Mga Kakulangan

• Hindi na ginagamit na may limitadong pangmatagalang pagkakaroon

• Mas mababang lohika at kapasidad ng memorya kumpara sa mga modernong FPGA

• Mas mabagal na bilis ng pagpapatakbo at pagganap ng I/O.

• Nangangailangan ng panlabas na memorya para sa pagsasaayos sa power-up

• Kulang sa mga advanced na tampok tulad ng mga bloke ng DSP at mga high-speed transceiver

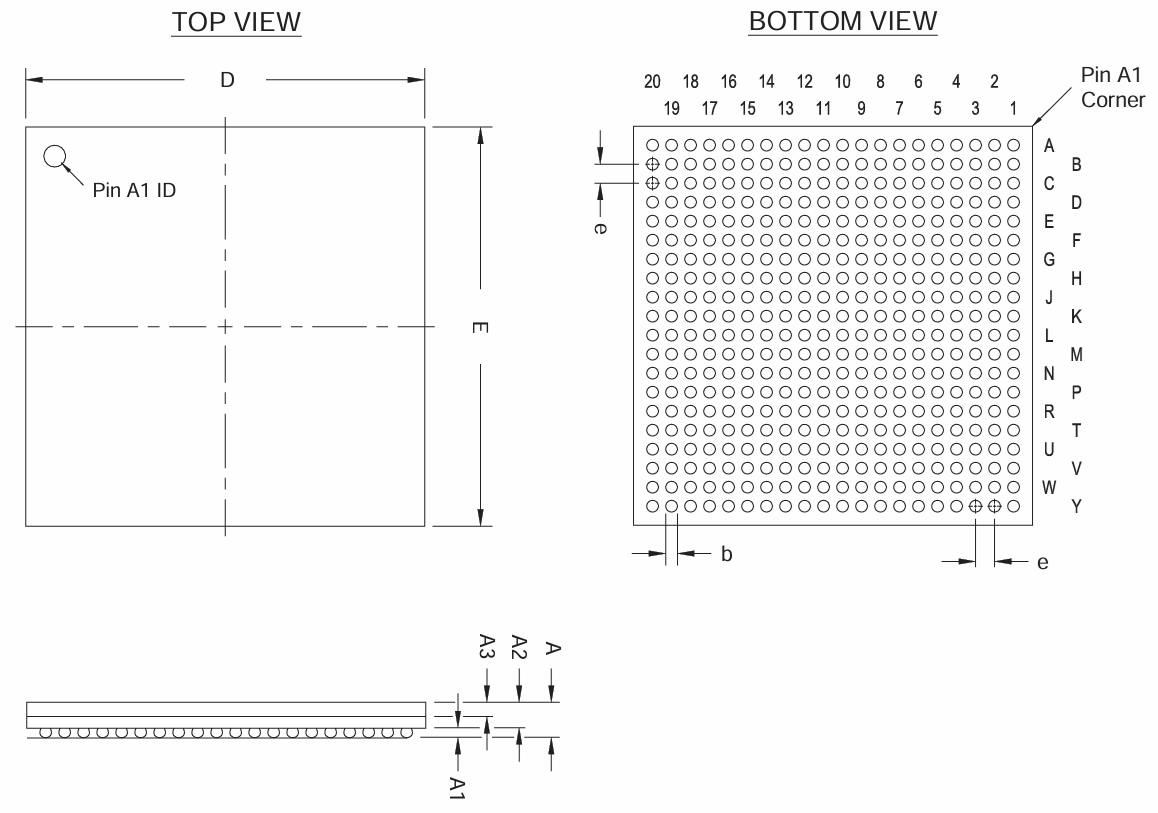

EP1C4F400C8 Mga Dimensyon ng Packaging

|

I -type |

Parameter |

|

Uri ng Package |

FBGA (fine-pitch ball grid array) |

|

Bilang ng bola |

400 |

|

Ball Pitch (e) |

1.0 mm (tipikal para sa Cyclone EP1C4F400) |

|

Diameter ng bola (b) |

0.45 mm (nominal) |

|

Laki ng Package (D × E) |

21 mm × 21 mm |

|

Taas ng pakete (a) |

2.40 mm (max) |

|

Kapal ng substrate (A2) |

~ 0.40 mm |

|

Amag na takip ng takip (A3) |

~ 1.90 mm |

|

Taas ng Ball (A1) |

0.25 mm (nominal) |

|

Pin A1 Corner |

Minarkahan para sa orientation |

|

Layout ng array |

20 × 20 grid (na may mga sulok na bola na nawawala) |

|

Pag -mount |

Surface Mount (SMD) |

Tagagawa ng EP1C4F400C8

Ang EP1C4F400C8 ay orihinal na ginawa ng Altera Corporation, isang payunir sa mga naka -program na aparato ng lohika at teknolohiya ng FPGA.Noong 2015, si Altera ay nakuha ng Intel Corporation, at ang linya ng produkto ay naging bahagi ng Intel's Programmable Solutions Group (PSG).Ngayon, sinusuportahan ng Intel ang mga legacy na Altera na aparato habang nakatuon ang pag -unlad sa mga mas bagong pamilya ng FPGA, tinitiyak ang pagpapatuloy para sa mga umiiral na mga gumagamit at pagsulong ng pagbabago sa programmable logic.

Konklusyon

Ang EP1C4F400C8 ay nakatayo bilang isang mahusay na gastos at maraming nalalaman FPGA na nag-aalok ng solidong pagganap para sa mga disenyo ng mid-range.Sa pamamagitan ng 4,000 mga elemento ng lohika, naka -embed na memorya, malawak na suporta sa I/O, at pagiging tugma na may maraming mga pamantayan sa boltahe at interface, nagbibigay ito ng kakayahang umangkop sa iba't ibang mga aplikasyon.Ang arkitektura nito, proseso ng programming, at malawak na kakayahang magamit sa DSP, mga naka -embed na system, at pagkuha ng data ay ginagawang isang praktikal na pagpipilian sa kabila ng katayuan ng pamana nito.Habang kulang ito ng mga advanced na tampok na matatagpuan sa mga mas bagong aparato at nahaharap sa limitadong pagkakaroon ng pangmatagalang pagkakaroon, nananatili itong isang maaasahang pagpipilian na naghahanap ng mga napatunayan na solusyon sa mga nasusukat na disenyo ng FPGA.

Datasheet PDF

EP1C4F400C8 DATASHEETS:

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Anong mga tool ang kinakailangan upang i -program ang EP1C4F400C8?

Kailangan mo ng software ng Quartus ng Intel (dati nang Altera Quartus II) kasama ang isang suportadong programming cable tulad ng USB-Blaster.Pinapayagan ka ng mga tool na ito na lumikha ng bitstream at i -load ito sa FPGA.

2. Maaari bang direktang hawakan ng EP1C4F400C8 ang mga aplikasyon ng PCI?

Oo, mayroon itong built-in na pagsunod para sa mga pamantayan sa PCI (33/66 MHz, 32/64-bit), na ginagawang angkop para sa pagsasama ng system na batay sa PCI nang hindi nangangailangan ng labis na lohika ng bridging.

3. Ano ang mangyayari kung ang EP1C4F400C8 ay nabigo sa pagsasaayos?

Kung nabigo ang pagsasaayos, ang conf_done pin ay hindi igiit ang mataas.Karaniwan itong tumuturo sa isang error sa file ng bitstream, pagkakasunud -sunod ng boltahe, o pag -setup ng pin, at dapat na muling suriin sa iyong daloy ng disenyo.

4. Maaari bang direkta ang interface ng EP1C4F400C8 sa memorya ng DDR?

Sinusuportahan nito ang ilang mga pamantayan sa I/O ngunit walang mga katutubong interface ng DDR tulad ng mga modernong FPGA.Ang mga karagdagang pagsasaalang -alang sa disenyo o mga sangkap ng bridging ay maaaring kailanganin.

5. Paano ihahambing ang EP1C4F400C8 sa mas bagong FPGAS?

Kumpara sa mga modernong aparato, ang EP1C4F400C8 ay may mas mababang bilis, mas kaunting lohika density, at mas kaunting mga advanced na tampok.Gayunpaman, nananatili itong isang mahusay na pagpipilian para sa matatag, mid-range na disenyo kung saan hindi kinakailangan ang pagganap ng paggupit.

EPM3256AFC256-7 Pangkalahatang-ideya ng CPLD: Mga Tampok, Pinout, Programming at Application

sa 2025/10/3

ADG432BR Analog Switch IC: Mga Pagtukoy, Pinout, Alternatibo at Datasheet

sa 2025/10/2

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147778

-

USB-C pinout at mga tampok

sa 2000/04/18 112035

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111352

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83794

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79602

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66978

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63111

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63044

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54097

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52198