Komprehensibong pangkalahatang -ideya ng UP/Down Counter: Disenyo ng Circuit at Paliwanag ng 74193 IC

Sa masalimuot na mundo ng digital electronics, ang mga counter ay gumaganap ng isang pangunahing papel sa sunud -sunod na disenyo ng circuit, na nagpapagana ng tumpak na tallying ng mga digital pulses sa iba't ibang mga aplikasyon.Ang mga pangunahing sangkap na ito ay pinapagana ng mga flip-flops (FF) na naka-synchronize na may mga signal ng orasan (CLK), tinitiyak ang maaasahang pagsubaybay at pagproseso ng temporal na data.Kung gumagana bilang hiwalay na mga aparato o bilang mga pangunahing bahagi ng mas malalaking sistema, ang mga counter ay naging isang kinakailangan sa digital na disenyo.Kabilang sa mga magkakaibang uri ng mga counter, ang mga pataas/down counter ay nakatayo para sa kanilang natatanging kakayahang mabilang sa parehong direksyon, na nag -aalok ng walang kaparis na kakayahang umangkop at kahusayan.Sa artikulong ito, naghuhukay kami sa mga mekanika, aplikasyon, at kabuluhan ng mga up/down counter, na may isang spotlight sa maraming nalalaman 74193 IC.Sa pamamagitan ng paggalugad ng kanilang papel sa aktwal na mga sistema at digital na mga makabagong ideya, naglalayong magbigay kami ng isang komprehensibong gabay para sa iyo.Catalog

Pag -unawa sa Up/Down Counter

Nag-aalok ang mga Up/Down counter ng isang masalimuot na paraan ng pagbibilang, na nagpapahintulot sa mga operasyon ng dalawahan-direksyon batay sa mga partikular na signal signal.Ang mga counter na ito ay matatagpuan sa mga aplikasyon kung saan ang pagbibilang pataas at pababa ay parehong kinakailangan, tulad ng nakikita sa mga teknolohiya ng TTL - tulad ng 74LS190 at 74LS191 - na marunong lumipat ng mga mode ng pagbibilang bilang tugon sa kanilang mga direktiba sa pag -input.

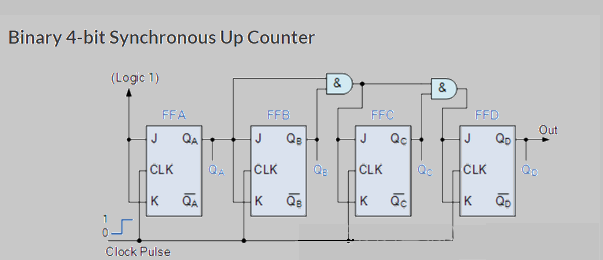

4-bit binary up/down counter

Ang 4-bit counter ay nagpapakita ng pagbibilang ng binary, husay na nag-navigate mula 0000 hanggang 1111 at nag-ikot ng paikot.Ang mga pulses ng orasan ay nagtutulak ng mekanismo ng pagdaragdag sa isang saklaw na 0-15, kasama ang bawat tik na pamamaraan na nag-uudyok sa isang kasunod na estado.

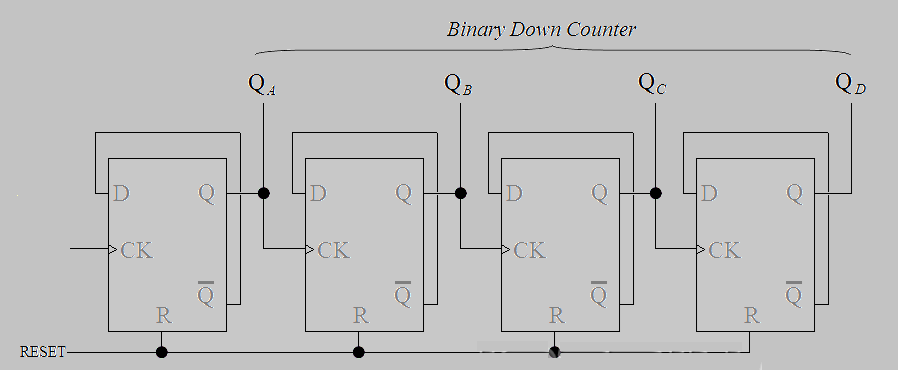

Sa kaibahan, ang proseso ng pag-decrement, na paglilipat mula 1111 hanggang 0000, ay nakasalalay sa apat na D-type na flip-flop na isinaaktibo ng mga gilid ng orasan.Ang makabagong paggamit ng mga baligtad na mekanismo ng feedback ay nakakamit ng isang maayos na interplay ng mga output, na nagtatampok ng parehong pagkamalikhain at katumpakan.

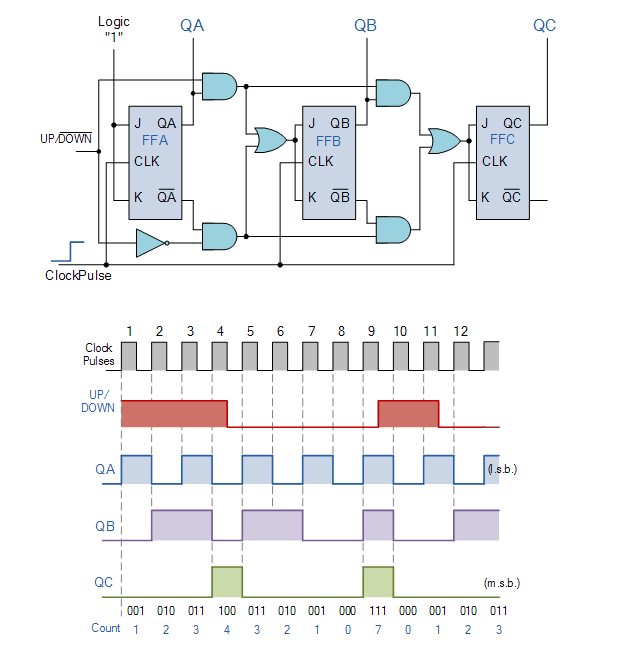

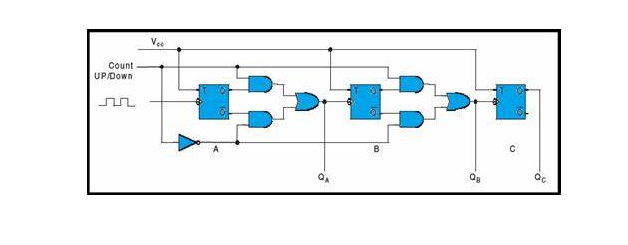

Kasabay na 3-bit up/down counter

Ang 3-bit na kasabay na counter, na gumagamit ng JK flip-flops, ay nagpapakita ng isang mahusay na diskarte sa pagbibilang mula 0 (000) hanggang 7 (111) at likod.Pinapayagan ng kasabay na disenyo nito para sa pino na kontrol sa proseso ng pagbibilang, kung saan ang bawat paglipat ng estado ay naayos sa pamamagitan ng tumpak na mga utos ng pag -input.Ang tampok na ito ay nagpapabuti ng kawastuhan sa up-counting mula 0 hanggang 7, habang walang tigil na pamamahala ng pagbagsak mula 7 pabalik sa 0.

Ang pagdidisenyo ng isang up/down counter circuit

Ang 3-bit counter circuit ay nakatayo bilang isang pangunahing elemento sa digital na disenyo, na naghahain ng magkakaibang bilang at mga layunin sa tiyempo.Patuloy itong gumagamit ng mga flip-flops (FF) upang matukoy ang direksyon ng bilang-naitala o bumababa.

Sa mode na up-count, ang bawat FF ay nakahanay sa isang pag-input ng orasan mula sa naunang output ng FF (Q), na gumagabay sa circuit sa isang maayos na pag-akyat sa pamamagitan ng mga binary state mula 000 hanggang 111. Ang pagkakasunud-sunod na ito ay madalas na nakakahanap ng pabor sa mga aplikasyon na hinihingi ang eksaktong tiyempokontrol, kabilang ang mga digital na relo at calculator kung saan ang kawastuhan ay nagbibigay ng kasiyahan at pagiging maaasahan.

Ang paglipat sa mode ng down-count ay hinihiling ng isang matalinong diskarte, na nakikibahagi sa mga kabaligtaran na output ng flip-flops.Paglihis mula sa isang simpleng pasulong na martsa, ang pagsasaayos na ito ay nag -redirect ng bawat pag -input ng orasan ng FF upang makatanggap ng mga signal mula sa pandagdag sa naunang output ng FF.Dahil dito, ang circuit ay binibilang sa baligtad, mula sa Binary 111 pabalik sa 000.

Mga mekanika ng Up/Down Counter

Ang pag -andar ng up/down counter ay nakasalalay sa isang control input na tumutukoy sa mode ng pagpapatakbo nito, na nagdidikta kung ang bilang ay umakyat o bababa.Ang kakanyahan ng operasyon nito ay namamalagi sa walang tahi na pag-sync sa pagitan ng output ng flip-flops (FFS) at kontrolin ang mga signal na nakakaapekto sa kasunod na mga FF.Sa mga aplikasyon, kahit na ang pinakamaliit na paglihis mula sa perpektong tiyempo ay maaaring humantong sa pagbibilang ng mga error, na binibigyang diin kung gaano kalaki ang pag -coordinate ng tiyempo ng signal.

• count-up mode

|

Estado |

QC |

QB |

QA |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

• count-down mode

|

Estado |

QC |

QB |

QA |

|

7 |

1 |

1 |

1 |

|

6 |

1 |

1 |

0 |

|

5 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

Sa isang tipikal na pagsasaayos, tatlong flip-flops ang nag-iimbak ng isang 3-bit na digital na halaga, na nagpapagana ng isang binary count na mula 0 hanggang 7. Maaari mong madalas na harapin ang mga hamon na pinapanatili ang pagiging maaasahan ng mga nakaimbak na halaga, lalo na kapag ang pakikitungo sa mga kapaligiran ay nag-aalsa sa ingay ng elektrikal o panghihimasok o pagkagambala.Upang malutas ang mga hamong ito, ang mga karagdagang pamamaraan ng pag -synchronize o pag -filter ay madalas na ginagamit, tinitiyak ang data na mapangalagaan na may integridad sa panahon ng mga paglilipat.

Ang mga logic gate ay makabuluhang nakakaapekto kung paano nakadirekta ang mga signal na ito, tinitiyak na ang counter ay sumusunod sa mga pangangailangan sa pagpapatakbo nito.Pinamamahalaan nila ang daloy upang matiyak na isang estado lamang - alinman sa pagdaragdag o pag -decrement - ay kumikilos ng aktibo sa anumang sandali.Ang mga advanced na circuit ay maaaring isama ang mga naka -program na lohika, nag -aalok ng pinahusay na kakayahang umangkop, at mga dinamikong pagsasaayos.Ipinakikilala nito ang isang nakakaintriga na aspeto: ang pagdidisenyo ng mga counter na may pananaw para sa scalability sa hinaharap ay maaaring makabuluhang mapalawak ang kanilang utility.

Pinino ang mga dinamikong tibok ng orasan gamit ang isang up/down counter

Ang isang up/down counter ay nagbabago ng mga estado sa pamamagitan ng pag-aayos ng mga flip-flop (FF) na mga output bilang tugon sa mga pagbabago sa tibok ng orasan.

• Sa senaryo ng up-counting: Ikonekta ang paunang flip-flop sa lohika 0, na nagiging sanhi ng pag-toggle sa pababang mga gilid ng orasan, pagpapahusay ng pag-synchronise na may mga layunin ng system para sa walang tahi na daloy.Ang mga saloobin na nagmula sa mga karanasan sa disenyo ng digital circuit ay nagmumungkahi na ang pagbabalanse ng mga pagkilos na ito ay maaaring mabawasan ang mga maling pag -trigger, sa gayon ang pagtaas ng pagiging maaasahan sa paglipas ng panahon.

Down-counting at maayos na paglipat ng estado

• Sa mode na down-counting: Kumonekta sa Logic 1 upang paganahin ang lahat ng mga flip-flops na i-toggle, na humahantong sa isang makinis na pagbawas mula sa mas mataas na estado.Ang pamamaraang ito ay maihahalintulad sa maingat na pag -ayaw ng isang tagsibol, kung saan ang katumpakan at tiyempo ay matiyak ang isang minimal na mekanikal na pilay sa panahon ng pagbabalik sa baseline.Ang pag -aayos na ito ay nagpapadali ng isang unti -unting pagbaba hanggang sa isang pagkakasunud -sunod ng pag -reset ay sinenyasan.

Mahusay na pag -reset ng ikot at katiyakan ng pare -pareho

Ang mga nakagawiang pag -reset ay nangyayari tuwing walong mga siklo ng orasan, tinitiyak ang pare -pareho na operasyon.Ang walong-cycle na balangkas ay nagbibigay ng isang tinukoy na yugto para sa bawat shift ng estado, tinitiyak na ang bawat yugto ay nakumpleto nang mahusay bago magsimula ang susunod.Ang feedback mula sa mga praktikal na aplikasyon ay nagmumungkahi na ang mga pana -panahong pag -reset na ito ay maiwasan ang mga pagkakamali sa pag -iipon, pagpapatibay ng balanse ng pagpapatakbo.

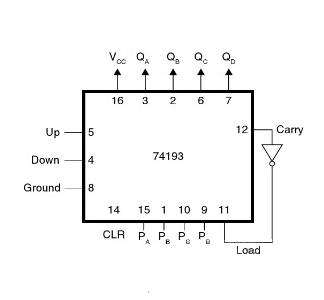

74193 UP/DOWN COUNTER IC Pangkalahatang -ideya

Ang 74193 Ang integrated circuit, na kilala bilang isang 4-bit na kasabay na binary counter, ay may kasamang namamahala sa parehong paitaas at pababang pagbibilang ng mga pag-andar.Ang kakayahang hawakan ang mga pagkakasunud -sunod ng pagbibilang hanggang sa isang modulo na 16 ay nagpapahiram mismo sa isang malawak na hanay ng mga digital na aplikasyon.Ang IC na ito ay natatanging dinisenyo gamit ang mga terminal na partikular para sa pataas at pababa, kasabay ng isang master reset at pag -load ng input, na nagbibigay ng kadalian sa pag -configure ng paunang estado ayon sa iba't ibang mga pangangailangan.

Ang arkitektura ng 74193 IC ay sumusuporta sa walang kahirap -hirap na pagbibilang ng direksyon.Sa mga digital na aparato, ang pagpili sa pagitan ng paitaas at pababang pagbibilang ay nagpapabuti sa kakayahang umangkop ng system.Ang bawat operasyon ng pagbibilang ay tiyak na nakahanay sa tibok ng orasan, ginagawa itong isang maaasahang pagpipilian para sa mga kumplikadong sistema kung saan ang tiyempo ay ang kakanyahan.Para sa iyo, ang pag -synchronize na ito ay maaaring maging isang madiskarteng kadahilanan sa pagtiyak ng pare -pareho na pagpapatupad ng pagkakasunud -sunod.

Ang isang pangunahing tampok ng IC na ito ay ang Master Reset, na nagbibigay -daan para sa agarang pag -reset ng lahat ng mga piraso - isang function na madalas na na -deploy sa panahon ng pagsisimula o kapag ang pagwawasto ng mga pagkakamali.Bukod dito, ang pag -input ng pag -load ay nagpapalaki ng pagiging kapaki -pakinabang nito sa pamamagitan ng pagpapagana sa iyo upang magtakda ng paunang natukoy na mga paunang bilang, na nagpapahintulot sa isang antas ng pag -personalize na kinakailangan sa iba't ibang mga digital na konteksto.Ang nasabing pag -personalize ay nagiging pangunahing sa mga senaryo kung saan ang mga aparato ay sumasailalim sa regular na pagsisimula o nangangailangan ng espesyal na paghawak sa panahon ng mga pagkagambala.

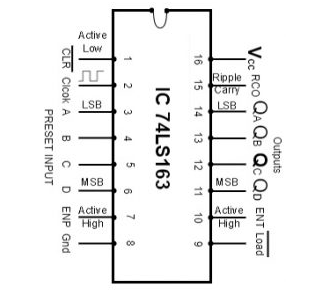

Pag -configure ng PIN

|

Numero ng pin |

Pangalan ng pin |

Paglalarawan |

|

Pin 1 |

Clr |

Isang aktibong-mababang pag-reset ng input. |

|

Pin 2 |

Clk |

Isang signal ng pag -input ng orasan. |

|

Pin 3 |

A (LSB) |

Data preset input. |

|

Pin 4 |

B |

Data preset input. |

|

Pin 5 |

C |

Data preset input. |

|

Pin 6 |

D (MSB) |

Data preset input. |

|

Pin 7 |

Enp |

Isang aktibong mataas na input na may label na ENP. |

|

Pin 8 |

Gnd |

Ground pin. |

|

Pin 9 |

Mag -load |

Isang aktibong-mababang pag-load ng data ng pag-load. |

|

Pin 10 |

Ent |

Isang aktibong mataas na input na may label na ENT. |

|

Pin 11 |

QD (MSB) |

Flip-flop output. |

|

Pin 12 |

QC |

Flip-flop output. |

|

Pin 13 |

QB |

Flip-flop output. |

|

Pin 14 |

QA (LSB) |

Flip-flop output. |

|

Pin 15 |

RCO |

Ripple Carry Output Transitioning mula 0 hanggang 1. |

|

Pin 16 |

VCC |

Power input pin. |

Mga tampok

|

Tampok |

Paglalarawan |

|

Dalas ng clk |

Nagpapatakbo ng isang dalas ng CLK na 32 MHz. |

|

Paggamit ng kuryente |

Ang paggamit ng kuryente ay nakulong sa 93 MW. |

|

Uri ng counter |

Function bilang isang 4-bit modulo-16 pataas/down counter. |

|

Preset input |

Ay may magagamit na mga preset na input. |

|

Programming |

Nagtatampok ng magkakasabay na programming. |

|

Ripple Carry |

Ay may panloob na ripple na dalhin para sa mahusay na pagbibilang. |

|

Magdala ng output |

Nag-aalok ng isang pagdala ng output na angkop para sa N-bit cascading. |

|

Oras ng pagpapalaganap |

Ipinagmamalaki ang isang oras ng pagpapalaganap ng 14 ns. |

Ang pagtatayo ng isang pataas/down counter kasama ang IC 74193

Ang kumplikadong 74193 IC, na kinikilala para sa mga adaptable na pag -andar ng pagbibilang nito, ay isang mahalagang sangkap sa mga digital system para sa pagpapagana ng maraming nalalaman/pababang pagbibilang ng mga gawain.Sa layout ng circuit, ang PIN-16 ay konektado sa VCC upang maibigay ang IC sa lakas ng pagpapatakbo.Ang mga malinaw na pin ay saligan na madiskarteng, na kumikilos upang i -reset ang counter kung kinakailangan, na tumutulong upang mapanatili ang pagiging maaasahan ng system at pagganap.

Ang data ng binary ay pumapasok sa IC sa pamamagitan ng PIN PA, PB, PC, at PD.Ang kaukulang mga output ng binary ay maaaring ma -access sa QA, QB, QC, at QD, na naghahatid ng mga naproseso na bilang na kadalasang kapaki -pakinabang para sa mga gawain tulad ng mga circuit circuit at dalas ng mga divider na humihiling ng mataas na katumpakan.

Ang bilang ng direksyon, kung ang pagdaragdag o pag -decrementing, ay kinokontrol sa pamamagitan ng mga dalubhasang pag -input ng orasan.Ang kakayahang ito ay nagbibigay -daan sa iyo upang pabagu -bago na ayusin ang pagkakasunud -sunod ng pagbibilang ng IC, pagpapahusay ng kakayahang umangkop sa iba't ibang mga aplikasyon.Kapag ginagamit ang IC sa mga praktikal na senaryo, ito ay nag -iingat na maingat na hubugin ang mga pulso ng orasan at tugunan ang mga isyu sa ingay upang maiwasan ang mga hindi tamang bilang, tinitiyak na ang circuit ay nagpapatakbo nang maaasahan.

Paghahambing na pagsusuri ng up counter at down counter

|

Up counter |

Down counter |

|

Ang up counter tallies mula sa '0' hanggang sa pinakamataas na limitasyon nito |

Ang down counter ay nagsisimula mula sa rurok na halaga nito at bumaba

sa '0' |

|

Binibilang nito ang mga kaganapan sa isang pataas na pagkakasunud -sunod |

Binibilang nito ang mga kaganapan sa isang pababang pagkakasunud -sunod |

Mga lakas at mga limitasyon ng Up/Down Counter

Lakas

Ang mga pataas/down counter ay nagbibigay ng iba't ibang mga benepisyo, lalo na sa mundo ng Pagsasama sa mga high-speed system.Ang kanilang prangka na flip-flop na istraktura ay tumutulong sa walang hirap na koneksyon, na madalas na humahantong sa mga pagpipilian na mahusay na gastos para sa mga digital na aparato kung saan ang pag-minimize ng pagiging kumplikado ay isang priyoridad. Ang kakayahang mabilang sa magkabilang direksyon - pababa at pababa - ay nagdudulot ng kakayahang umangkop, nagpapatunay na kapaki -pakinabang sa mga aplikasyon tulad ng mga digital na orasan o mga counter ng kaganapan kung saan kanais -nais ang pagbibilang ng bidirectional. Bilang karagdagan, ang kanilang pag -andar ay nagniningning sa mga sistema ng pagsubok na ginamit para sa pagkumpirma ng mga lohikal na signal.Pinahahalagahan ng mga application ng hands-on ang kanilang hindi komplikadong disenyo, na nagsisiguro ng mas simpleng pag-debug at pagpapanatili, na nag-aalok ng isang kapansin-pansin na kalamangan para sa iyo na nakatuon sa paglutas ng problema at pag-optimize.

Mga limitasyon

Sa kabila ng mga lakas, ang mga counter ng pataas/down ay nagpapakita ng mga partikular na limitasyon, lalo na tungkol sa katumpakan sa mga nakataas na frequency. Habang tumataas ang bilis ng pagpapatakbo, maaari silang makatagpo ng mga kawastuhan, na nagdudulot ng mga hamon sa mga system na unahin ang mataas na pagiging maaasahan. Ang mga kawastuhan na ito ay madalas na nagmula sa pag -asa sa panlabas na pag -synchronise ng orasan, na maaaring partikular nangangailangan ng pandagdag na mga flip-flop circuit.Ang ganitong mga kinakailangan ay maaaring Dagdagan ang pagiging kumplikado ng circuit at ipakilala ang mga potensyal na pagkaantala sa tiyempo.Bukod dito, kapag namamahala ng masalimuot na mga sistema ng bit, Ang anumang mga pagkaantala na nauugnay sa mga counter ay maaaring magpalala, nakakaapekto sa pangkalahatang pagganap ng system.Dahil dito, maaari mong madalas na galugarin ang mga alternatibong solusyon o karagdagang mga sangkap upang mabawasan ang mga epektong ito, na batayan ang kanilang mga diskarte sa pinabuting pamamaraan ng pag -synchronize.Ang pag -navigate sa mga kompromiso na ito ay hinihiling ng isang maalalahanin na pagsusuri ng mga pangangailangan ng system at kung paano maaaring makaapekto sa pagganap ang mga naturang elemento, madalas na dumadaan sa iyo patungo sa mga istratehikong pagpapahusay ng disenyo na naaayon sa mga tiyak na kahilingan sa aplikasyon.

Gumagamit ng Up/Down Counter

Mga counter ng auto-reversing

Sa World of Systems Engineering na hinihiling ng masusing kontrol, ang mga UP/Down counter ay nagpapakilala ng isang kapaki -pakinabang na tampok: ang awtomatikong pagsasaayos ng pagbibilang ng direksyon sa mga limitasyon ng itinakda.Ang kakayahang umangkop na ito ay sumusuporta sa isang walang kamali -mali na paglipat sa pagitan ng pasulong at paatras na pagbibilang.Ang nasabing pag -andar ay lalo na pinahahalagahan sa mga awtomatikong kapaligiran kung saan ang pagsubaybay sa paggalaw sa parehong direksyon ay malalim na nakakaapekto sa kahusayan sa pagpapatakbo.Halimbawa, ang mga pang -industriya na robotics, ay gagamitin ang katangiang ito upang matiyak ang kawastuhan pagkatapos maabot ang kanilang mga hangganan ng paggalaw.

Mga Divider ng Clock

Sa loob ng mga digital na elektronikong sistema, ang mga counter ng pataas/down na kontribusyon ay malaki ang naiambag sa katha ng mga divider ng orasan, na marunong magbago ng dalas ng mga signal ng orasan.Ang modyul na ito ay tumutulong sa pagtatayo ng mga signal ng tiyempo na susi para sa pagmamaneho ng magkakaibang mga sangkap sa iba't ibang mga frequency sa loob ng isang integrated system.Sa pamamagitan ng pag -aalok ng mga orasan ng magkakaibang bilis, ang mga counter na ito ay gumaganap ng isang pangunahing papel sa pag -synchronize ng iba't ibang mga proseso, sa gayon ay nagbibigay -kasiyahan sa mga natatanging pangangailangan ng system.

Mga Sistema sa Pamamahala ng Paradahan

Sa mga puwang ng lunsod na choked na may trapiko, ang mga pataas/down counter ay naghahatid ng mga dynamic na solusyon sa pamamagitan ng mga sistema ng pamamahala ng paradahan.Sa pamamagitan ng pamamaraan na pagtaas ng bilang sa pagpasok ng bawat sasakyan at pagbawas nito sa paglabas, ang mga counter na ito ay nagbibigay ng napapanahong pag -update sa magagamit na mga paradahan.Ang aktwal na mekanismo ng pagsubaybay na ito ay sumusuporta sa mahusay na paggamit ng imprastraktura ng paradahan habang pinayaman ang iyong karanasan.

Dalas ng pagkahati

Para sa mga gawain na kinasasangkutan ng dalas ng pagkahati sa mga network ng komunikasyon, ang mga counter ng pataas/pababa ay nagpapatunay na lubos na kapaki -pakinabang dahil sa kanilang mababang ingay at nabawasan ang pagkonsumo ng kuryente.Ang mga counter na ito ay tumutulong sa masusing dibisyon at pamamahala ng mga frequency, na nagpapagana ng tirahan ng maraming mga channel sa loob ng isang network.Sa mga kapaligiran na may malawak na pagproseso ng signal, ang paggamit ng mga naturang counter ay nagsisiguro ng kaunting pagkagambala, pagpapanatili ng integridad at kalidad ng mga signal ng komunikasyon.

Asynchronous Decadal Bilang

Ang mga Up/Down counter ay nagbibigay -daan sa pagbibilang ng asynchronous decadal, na ginagamit para sa mga aplikasyon kung saan naganap ang mga operasyon nang nakapag -iisa ng mga pandaigdigang orasan.Sa mga asynchronous system, ang mga counter na ito ay nagbibigay ng isang maaasahang diskarte upang makamit ang pagbibilang ng base-10, napakahusay sa kakayahang umangkop nang walang pag-alis ng katumpakan.Ang kanilang utility ay nagniningning sa mga system na nagpapatakbo sa iba't ibang mga kondisyon, maayos na pagsasaayos nang hindi nagsasakripisyo ng kawastuhan.

Konklusyon

Ang artikulong ito ay naghuhukay sa masalimuot na disenyo at mga aspeto ng pagpapatakbo ng up/down counter, na nakatuon sa 74193 IC.Kilala sa dalawahan nitong mga kakayahan sa pagbibilang - parehong pataas at pababang - mayroon itong magkakaibang mga aplikasyon, mula sa sopistikadong mga sistema ng paradahan hanggang sa masalimuot na mga gawain sa dibisyon ng dalas.Tulad ng paglilipat ng mga teknolohikal na landscape, ang isang malalim na pag -unawa sa mga sangkap na ito ay maaaring magmaneho ng pagbabago at mapalakas ang kahusayan.Ang utility ng Up/Down Counter ay umaabot sa kabila ng maginoo na mga aplikasyon, na nakikipagsapalaran sa mga awtomatikong sistema kung saan ang tumpak na pagbibilang ng mga mekanismo ay nagpapaganda ng pagiging epektibo.Halimbawa, sa mga dynamic na solusyon sa pamamahala ng trapiko, ang mga naturang counter ay naglalaro ng isang pangunahing papel sa pamamagitan ng pagsasama ng aktwal na data upang ma -optimize ang daloy.Ang pag -agaw ng kakayahang magamit ng aparato ay nagbibigay -daan sa mga hamon sa iba't ibang sektor na matugunan ng mga na -customize na diskarte.Mula sa mga pananaw na partikular sa industriya, ang eksaktong pagpapatupad ng mga counter na ito ay maaaring makabuluhang mapalakas ang pagganap ng system.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Madalas na nagtanong [FAQ]

1. Ano ang teorya sa likod ng isang 8-bit up/down counter?

Ang isang 8-bit up/down counter ay humahawak ng isang 8-bit digital signal, na nagpapatunay na kapaki-pakinabang sa mga arkitektura ng disenyo tulad ng mga digital-to-analog converters (DAC) at mga decoder.Ito ay madalas na nagtatampok ng mga pagpapakita ng LED at nagsasangkot ng pagsasaayos sa pamamagitan ng walong mga pin.Ang kakayahang umangkop ng counter ay naka -highlight sa pamamagitan ng paggalugad ng mga digital na pagpoproseso ng signal, kapaki -pakinabang sa parehong sopistikadong mga sistema ng computational at mas simpleng aparato.Ang pagpapatupad ng mga counter na ito ay karaniwang nangangailangan ng maingat na pansin sa integridad ng signal at pag -setup ng mga nuances.

2. Paano ginagamit ng isang up/down counter ang JK flip-flops?

Ang 4-bit counter na ito ay gumagamit ng magkakasabay na operasyon na may JK flip-flops upang mabago ang direksyon ng pagbibilang batay sa estado ng lohika ng up/down input.Tumugon ito sa mga pulso ng orasan, habang ang pagpapagana ng input ay nagsisilbing isang aktibong mekanismo ng kontrol.Maaari mong pagsamantalahan ang disenyo na ito upang matiyak ang maaasahang tiyempo at sunud -sunod na pagganap sa iba't ibang mga aplikasyon, na naglalarawan ng pagiging epektibo ng magkakasabay na mga digital system.Ang pag -unawa sa mga sopistikadong sistemang ito ay maaaring mag -alok ng mas malawak na pananaw sa mga digital na circuit at magbigay ng inspirasyon sa mga makabagong solusyon sa disenyo ng lohika.

3. Ano ang nakikilala sa 74192 counter mula sa 74193 counter?

Ang 74192 ay kumikilos bilang isang counter ng dekada ng BCD, at ang 74193 ay gumaganap bilang isang 4-bit na kasabay na binary counter.Parehong naayon para sa iba't ibang mga tungkulin sa loob ng mga digital electronics.Kinikilala ang mga natatanging tampok ng bawat counter sa pagpili ng mga angkop na sangkap para sa magkakasabay na mga gawain sa pagbibilang.Ang nasabing mga desisyon sa disenyo ay maaaring makabuluhang maimpluwensyahan ang kahusayan sa pagpapatakbo at pagkakaisa sa mga kumplikadong circuit, na nag -aalok ng mahalagang pananaw para sa pag -optimize ng pinagsamang disenyo ng system.

4. Paano tinukoy ang isang 2-bit up/down counter?

Ang isang 2-bit up/down counter ay naglalakad ng isang simpleng pagkakasunud-sunod ng binary mula 0 hanggang 3, na gumagana sa parehong paitaas at pababang mga order.Ang operasyon na ito ay nagtatampok ng panghuli lohikal na mga prinsipyo at ang pagiging simple na posible sa mga digital system.Ang nasabing mga counter ay nagsisilbing malinaw na mga halimbawa ng binary aritmetika, na nag -aalok ng mga praktikal na karanasan sa pag -aaral na nagpapaganda ng mga modelo ng pang -edukasyon at mapadali ang pagsubok sa aparato, sa gayon pinalalalim ang pag -unawa sa mga operasyon ng binary.

5. Paano gumagana ang CD4029 counter?

Ang counter ng CD4029 ay nagpapatakbo ng kakayahang umangkop, na may kakayahang magbilang ng binary at dekada.Nag-preset ito sa pamamagitan ng mga input ng jam sa pagtanggap ng isang mataas na pag-aari ng signal at pag-reset sa zero kapag ang mababang paganahin ay nakikibahagi.Sinusuportahan ng kakayahang ito ang mga aplikasyon na hinihingi ang tumpak na mga pagsasaayos ng pagproseso ng signal.Ang praktikal na kaalaman sa operasyon nito ay nagsisiguro na ang CD4029 ay maaaring maayos na hawakan ang mga pag -reset at mga paglipat ng mode, na sumasalamin sa isang komprehensibong pag -unawa sa mga dinamikong kontrol sa mga digital na circuit.

Ang panghuli gabay sa module ng SX1262 chip

sa 2024/11/29

Komprehensibong paghahambing: LM324 vs LM358 pagpapatakbo ng mga amplifier

sa 2024/11/28

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147764

-

USB-C pinout at mga tampok

sa 2000/04/18 111987

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111351

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83751

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79542

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66949

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63089

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63028

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54092

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52172