Isang komprehensibong gabay sa protocol ng komunikasyon ng SPI

Sa artikulong ito, tuklasin namin ang mga detalye ng serial peripheral interface (SPI) protocol, na nakatuon sa mahusay na mga kakayahan sa paglilipat ng data at maraming nalalaman na mga aplikasyon.Ang SPI ay isang high-speed, kasabay na protocol ng komunikasyon na malawakang ginagamit sa mga naka-embed na system upang ikonekta ang mga microcontroller na may iba't ibang mga peripheral.Sa pamamagitan ng pagsasaayos ng master-alipin nito at apat na pangunahing linya-MISO, MOSI, SCLK, at CS-pinasimple ng SPI ang komunikasyon ng data habang tinitiyak ang pag-synchronise sa mga aparato.Kami ay maghuhukay sa mga pangunahing prinsipyo ng SPI, kabilang ang mga dinamikong pagpapatakbo, pagsasaayos ng hardware, mga diagram ng tiyempo, at praktikal na payo sa pag -setup.Kung bago ka sa SPI o naghahanap upang pinuhin ang iyong pag -unawa, ang post na ito ay magbibigay ng mahalagang pananaw sa pag -maximize ng potensyal nito sa aktwal na mga aplikasyon.Catalog

Pangkalahatang -ideya ng SPI Protocol

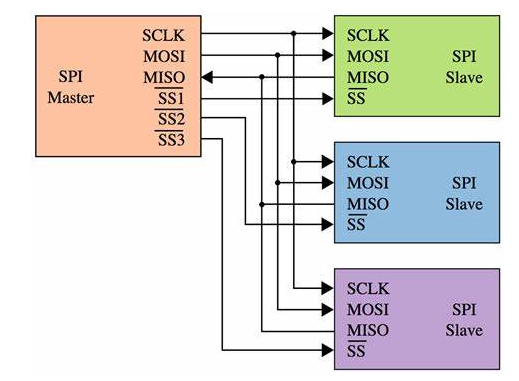

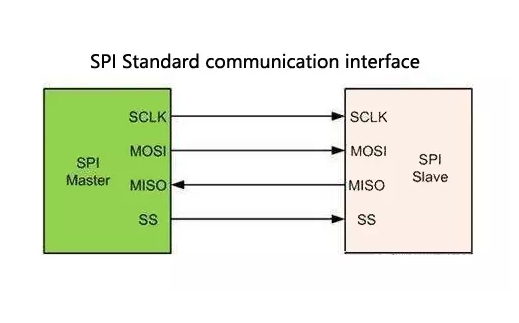

Ang serial peripheral interface (SPI) ay gumagamit ng isang 4-wire system na nag-streamlines ng mga operasyon ng CPU sa pamamagitan ng pagbabawas ng software overhead.Kilala sa bilis at kahusayan nito, ang SPI ay pangunahing sa mga aparato tulad ng AT91RM9200.Sa balangkas ng Master-Slave, pinamamahalaan ng Master ang mga gawain sa pamamagitan ng pakikipag-ugnay sa mga alipin sa pamamagitan ng apat na kinakailangang mga wire: MISO (Master in Slave Out), Mosi (Master Out Slave In), SCLK (Serial Clock), at CS (Chip Select).Ang mga linya ng MISO ay naglalagay ng data pabalik sa master, habang pinamamahalaan ng MOSI ang papalabas na data.Nagbibigay ang SCLK ng mga signal ng orasan mula sa master, at pinadali ng CS ang kontrol sa pag -activate ng aparato.Ang pagiging simple ng SPI ay ginagawang kadalasang kapaki -pakinabang para sa pagkonekta ng maraming mga aparato sa isang solong bus, pagpapatupad ng data transfer ng paglipat, at pagkamit ng pag -synchronize sa pamamagitan ng mga pulso ng orasan.Dito, ang master ay maaaring mag -pause ng komunikasyon nang hindi nakakaapekto sa pagiging maaasahan ng data.Habang ang SPI ay kulang sa control control at mga tampok ng pagkilala sa data, ang kakayahang dagdagan ang mga koneksyon sa peripheral sa pamamagitan ng mga panlabas na decoder ay nagbabayad para sa mga limitasyong ito.

Tukoy na mga pagkakataon ng paggamit ng SPI

Ang SPI ay itinayo sa paligid ng isang natatanging pag -setup ng bus ng singsing gamit ang mga bahagi tulad ng SS (CS), SCK, SDI, at SDO para sa pagpaparehistro ng data exchange.Ang isang 8-bit na paglipat ng rehistro, halimbawa, ay gumagamit ng mga gilid ng orasan upang pamahalaan ang paggalaw ng data at magrehistro ng mga paglilipat.Ang pagsisimula sa isang pag-setup ng master-alipin ay nagsisimula sa pre-configure transceiver buffers, na naglalarawan sa proseso ng komunikasyon.Ang Motorola's SPI ay nangunguna sa magkakasabay na serial na komunikasyon, na gumagamit ng MOSI, MISO, at SCK para sa mga advanced na gawain ng pagpapadala, kakayahang umangkop sa mga tungkulin ng Master-Slave, at matatag na pag-andar ng orasan.Ang mga aparato ay dapat i -synchronize ang phase ng orasan at polarity para sa pagkakapare -pareho ng komunikasyon.Sa kapasidad na mag-link ng hanggang sa 256 port, ang mga sentro ng SPI sa point-to-point na koneksyon at paglilipat ng data na nakabatay sa packet.

Pagbabalangkas ng lohika ng gumagamit

Ang pagdidisenyo ng adaptable na lohika ng gumagamit ay pabago-bago para sa mga aplikasyon na nagtatampok ng mga istruktura ng multi-port.Sa loob ng isang dual-port na pagsasaayos, ang mga independiyenteng FIFO ay humahawak ng data na may kaugnayan sa mga address ng port.Kasabay nito, ang logic arbitration ay nangangasiwa ng data ng data sa interface ng SPI4, na akomodasyon ng agarang data ng control control at mga katayuan ng FIFO.

SPI Operational Dynamics

Ang SPI ay inhinyero para sa maaasahang komunikasyon, na nagtatampok ng mga discrete channel para sa data at control ng daloy sa paghahatid.Ang malawak na koneksyon ng port ay nagpapahintulot sa mga paglilipat ng data na nakabatay sa packet, tinitiyak ang pagpapatunay ng point-to-point sa pamamagitan ng mga address ng packet, sa gayon pagpapalawak ng kakayahang magamit ng application.

Pag -aaral ng mga diagram ng paglilipat ng data

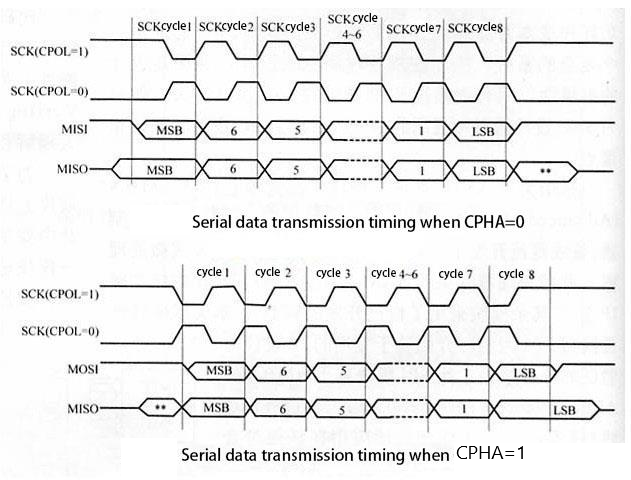

Ang mga interface ng SPI ay nailalarawan sa pamamagitan ng apat na mga diagram ng tiyempo na nakasalalay sa mga setting ng CPOL at CPHA.Tinukoy ng CPOL ang idle state para sa SCK, samantalang ang CPHA ay nagtatalaga ng sampling clock edge.Ang mga pagsasaayos na ito ay aktibo para matiyak ang kawastuhan at pag -synchronise ng data.

PAGSUSULIT NG PAGSUSULIT SA SERIYON

Pinagmulan ng Motorola, ang SPI ay nakatayo bilang isang apat na wire, bidirectional serial bus na ininhinyero para sa mabilis na magkakasabay na komunikasyon, na nag-uugnay sa mga microcontroller sa mga peripheral tulad ng EEPROM, RTC, at A/D Converters.Ang network ng SPI ay may kasanayang nag-uugnay sa mga halo-halong peripheral, na gumagamit ng mga protocol na pumipigil sa mga mekanismo ng address para sa direkta, buong-duplex na palitan.Ang mga karagdagang linya tulad ng INT ay maaaring mapabuti ang pagtugon ng system.

Mga Intricacies sa Pag -configure ng Hardware

Sa kabila ng kasanayan ng SPI sa pakikipag -ugnay sa iba't ibang mga peripheral, ang indibidwal ay nagbibigay -daan sa mga signal para sa bawat aparato na resulta sa pagiging kumplikado kumpara sa mas simpleng mga sistema tulad ng I2C.Ang pagiging kumplikado na ito ay isang intrinsic na aspeto ng pagsasaayos ng hardware ng SPI, na isinasama ang mga rehistro ng shift para sa 8-bit na paglilipat ng data.Sa panahon ng operasyon, ang mga aparato ay ligtas na lumipat ng mga piraso sa pamamagitan ng mga rehistro gamit ang pagbagsak ng orasan.

Pagsusuri ng kapasidad at pagiging praktiko

Ang paggamit ng mga elemento tulad ng spiclk, mosi, miso, at NSS, ang mga network ng SPI ay nagtatag ng mga tungkulin ng master-slave batay sa mga estado ng NSS pin.Ang pagsuporta sa solong o multi-master na kapaligiran, ang protocol ay umaangkop upang makontrol ang hanggang sa 16 na peripheral.Bagaman kulang ito ng control control at mga pamamaraan ng pagkilala, ang istraktura ng protocol ay mahusay na tinatanggap ang magkakaibang mga pag -setup ng koneksyon at komunikasyon.

Mga guhit ng pag -setup at tiyempo

Ang mga transaksyon ng data ng SPI ay kinokontrol ng diretso na mga patakaran sa tiyempo na naiimpluwensyahan ng pamamahala ng SCK.Halimbawa, ang isang pattern ng rehistro tulad ng 10101010 ay nagpapadala ng data nang bit-bit sa pamamagitan ng mga shift na hinihimok ng orasan, na itinatampok ang pagiging simple ng pagpapatakbo at dinamika ng paglipat ng data sa singsing ng bus.

Pinalawak na pananaw sa pagganap

Ang wastong pag -synchronise ng phase ng orasan ng SPI at polarity sa buong mga aparato ng master at alipin ay ginagamit para sa patuloy na mga transaksyon ng data.Ang mga parameter tulad ng CPOL at CPHA ay dapat na magkahanay sa pagitan ng mga aparato sa loob ng mga sistema na nauugnay sa SPI upang mapanatili ang pagkakaisa ng komunikasyon.

Praktikal na payo sa pag -setup

Ang mga pagsasaayos sa mga pagsasaayos ng orasan ng SPI ay kailangang isaalang -alang ang mga kahilingan sa orasan ng alipin upang matiyak ang kawastuhan ng data sa panahon ng mga siklo ng paglipat.Ang pagkilala sa mga gilid ng signal sa panahon ng paglilipat ng data ay seryoso upang maiwasan ang mga pagkakapare -pareho ng magkakaugnay.Ang mga manu-manong produkto ay madalas na detalyadong kinakailangang mga setting, na binibigyang diin ang epekto ng tumpak na pag-align ng pagkahulog sa paghahatid ng kawastuhan.

Mga pangunahing kaalaman sa komunikasyon ng SPI

Sa core nito, ang serial peripheral interface (SPI) ay nagsisilbing isang full-duplex, kasabay na serial protocol ng komunikasyon, na kinakailangan ng pag-aayos ng una para sa pakikipag-ugnay.Ang tampok na ito ay nagtatakda ng SPI bukod sa pamamagitan ng likas na pag -highlight ng mga naka -synchronize na palitan.Ang isang kilalang aspeto ng SPI ay ang pag-asa sa isang modelo ng master-slave, kung saan ang master aparato ay nag-orkestra ng kontrol sa pamamagitan ng pagbuo ng mga signal ng orasan at pagsisimula ng mga sesyon ng komunikasyon.Sa kaibahan, ang mga aparato ng alipin ay nananatiling nakatutok sa mga senyas na ito, na nakilahok upang lumahok kapag tinawag.

Ang mekanismo ng pakikipagtulungan sa pagitan ng mga aparato ng master at alipin sa loob ng SPI ay maingat na naayos.Ang Master ay humahawak ng eksklusibong responsibilidad para sa pamamahala ng orasan, tinitiyak ang isang matatag na ritmo para sa mga palitan ng data.Ang oversight na ito ay nag -streamlines ng pag -synchronize, na tinanggal ang hindi mahuhulaan na madalas na naroroon sa mga asynchronous system.Sa pamamagitan ng pagtatatag ng isang pinag -isang sanggunian ng oras, ang parehong mga aparato ay maaaring magsagawa ng mga operasyon na may kawastuhan, isang kasanayan na pinino sa pamamagitan ng malawak na karanasan sa aplikasyon.Ang maayos na likas na katangian ng SPI ay nagbibigay ng mahusay na mga kakayahan sa paglilipat ng data, na nagtatanghal ng isang prangka na alternatibo sa mas masalimuot na mga protocol.

Ang balangkas ng SPI ay nagpapakita ng mga partikular na hadlang, lalo na sa mga setting na binibigyang diin ang kadalian ng plug-and-play.Ang hindi nababaluktot na kalikasan ng protocol nito ay nangangahulugang pagiging tugma ay dapat na maingat na isagawa nang maaga.Ang mga aparato sa loob ng isang pag -andar ng pagsasaayos ng SPI sa ilalim ng awtoridad ng mga signal ng orasan at paunang natukoy na mga kasunduan sa protocol.Bagaman pinapadali nito ang pag -synchronize, hinihiling nito ang paunang pagsisikap sa pag -setup.Ang mahusay na aplikasyon ng mga alituntuning ito ay nagpakita ng potensyal na maibsan ang mga pagkakaiba -iba ng komunikasyon.Tulad ng naobserbahan sa mga pagsusuri sa session, ang isang pagkakahawak ng istruktura ng SPI ay hindi lamang nagpapabuti sa praktikal na paglawak ngunit pinalalaki din ang kawastuhan ng aplikasyon.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Lahat tungkol sa UDP: Isang Gabay sa Koneksyon na Walang Koneksyon

sa 2024/12/30

Teknolohiya ng HD: Pagpapahusay ng visual na kahusayan

sa 2024/12/30

Mga sikat na post

-

Complex Instruction Set Computers: Paano nila binago ang computing?

sa 8000/04/18 147758

-

USB-C pinout at mga tampok

sa 2000/04/18 111939

-

Gamit ang Xilinx Unified Simulation Primitives: Isang komprehensibong gabay sa disenyo ng FPGA at kunwa

sa 1600/04/18 111349

-

Mga Voltahe ng Power Supply sa Electronics: Kahulugan ng VCC, VDD, VEE, VSS, at GND

sa 0400/04/18 83721

-

RJ45 Gabay sa Konektor: Pinout, mga kable, mga uri ng cable, at paggamit

sa 1970/01/1 79508

-

Ang panghuli gabay sa mga code ng kulay ng kawad sa mga modernong sistema ng elektrikal

Ang paraan ng paggamit ng aming mga de -koryenteng sistema ay hindi lamang para sa mga hitsura.Ang bawat kulay ng kawad ngayon ay nagpapahiwatig ng isang tiyak na pag -andar, na ginagawang mas mada...sa 1970/01/1 66914

-

Purge Valve Guide: Function, sintomas, pagsubok, at kapalit para sa pinakamainam na pagganap ng engine

Ang balbula ng purge ay isang pangunahing bahagi ng sistema ng kotse na tumutulong na mapanatiling malinis ang hangin sa pamamagitan ng pamamahala ng mga singaw ng gasolina bago sila makatakas sa k...sa 1970/01/1 63062

-

Kalidad (Q) Factor: Mga Equation at Application

Ang kalidad na kadahilanan, o 'Q', ay mahalaga kapag sinusuri kung gaano kahusay ang mga inductors at resonator sa mga elektronikong sistema na gumagamit ng mga frequency ng radyo (RF).Sinusukat ng...sa 1970/01/1 63012

-

Pagkamit ng pagganap ng rurok na may maximum na teorema ng paglipat ng kuryente

Ang maximum na teorema ng paglipat ng kuryente ay nagpapaliwanag kung paano ang enerhiya mula sa isang mapagkukunan, tulad ng isang baterya o generator, ay dumadaloy sa isang konektadong pagkarga.I...sa 1970/01/1 54081

-

A23 Mga pagtutukoy ng baterya at pagiging tugma

Ang baterya ng A23 ay isang maliit, hugis-silindro na baterya na may mataas na boltahe.Tinatawag din ang 23A, 23AE, o MN21, tumatakbo ito sa 12 volts at mas mataas kaysa sa mga baterya ng ...sa 1970/01/1 52132